#### Lecture 5 Processor and Bus

Fetch-Execute Cycle Processor States Exceptions and Interrupts Program Placement in Memory

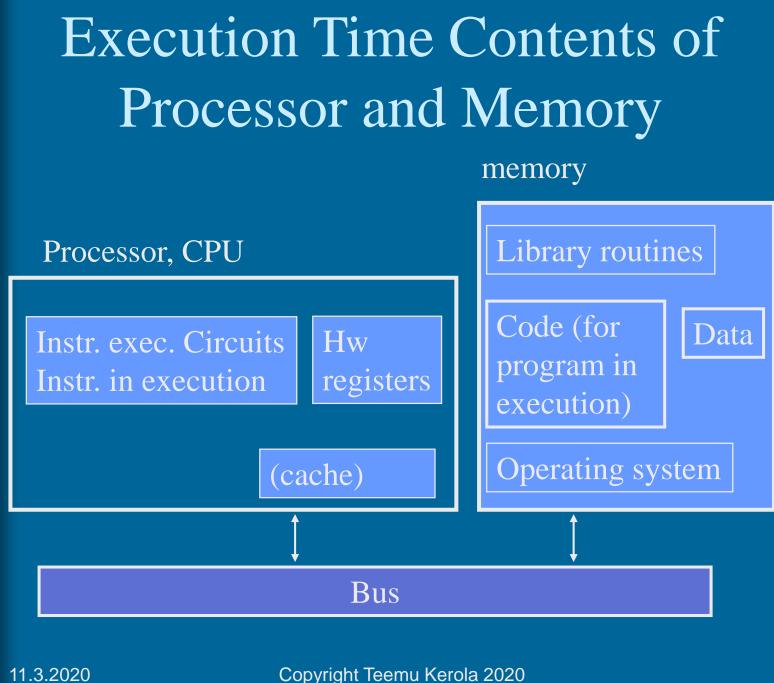

## **Processor Operation**

3

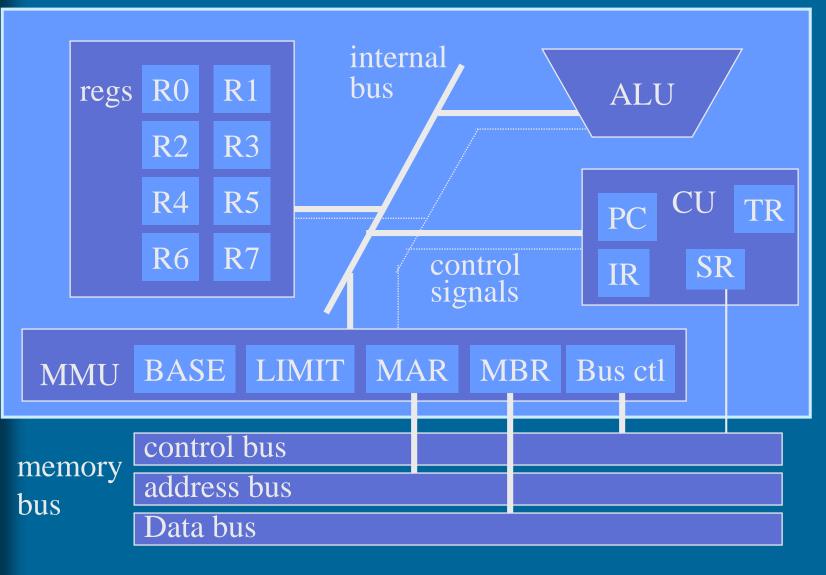

## TTK-91 Processor Structure

#### Break Instruction to Fields, and Compute Effective Address (EA)

| OPER opcode<br>8 bit field | ,  |    | Ri<br>3 bit | ADDR address, constant<br>16 bit field |

|----------------------------|----|----|-------------|----------------------------------------|

| 31       24                | 21 | 19 | 16          | 15                                     |

- Fields can be read with special wires from instr. reg (IR)

- Compute EA, result to TR

- Rj: 1st operand and result reg

- if Ri=0, then  $TR \leftarrow ADDR$

- else TR  $\leftarrow$  (Ri)+ADDR

- Do addition in ALU (or some special circuit)

- If ADDR = 0, niin TR  $\leftarrow$  (Ri)

- Now, Effective Address (EA) is in TR

- You can use contents of TR as is, as address of data in memory, or as indirect address of data in memory

- 2nd operand definition, use M to decide on how TR data is used

Instruction Execution Titokone visualization shows phases in simulation Store R4, @10(R1) ; R1 = 20, R4 = 15 – Instruction fetch and incrementing PC • PC  $\rightarrow$  MAR, <u>"bus read"</u>, wait for "mem  $\rightarrow$  MBR" • MBR  $\rightarrow$  IR •  $PC+1 \rightarrow PC$ - E.g., PC  $\rightarrow$  ALU1, 1  $\rightarrow$  ALU2, +, wait, ALU  $\rightarrow$  PC - E.g., PC  $\rightarrow$  INCin, wait, INCout $\rightarrow$  PC (own circuit) – Instruction execution phase •  $R1 \rightarrow ALU1, 10 \rightarrow ALU2, +, (odota), ALU \rightarrow TR$ • TMP  $\rightarrow$  MAR, <u>"bus read"</u>, wait for "mem $\rightarrow$ MBR"  $MBR \rightarrow MAR, R4 \rightarrow MBR,$ <u>"bus write"</u>, wait for "MBR $\rightarrow$ mem" – Total 3 memory references (this instruction) 11.3.2020 Copyright Teemu Kerola 2020

6

## TTK-91 Machine Code

OpcodeRjMRiAttribute (constant, addr)8 b3 b2 b3 b16 b

- Each instruction is 32 bits

- Each instruction has opcode

- How to interpret registers and attribute, depends on opcode and mode (M)

- Data types:

- 32-bit integer, or raw 32-bit values

- No floating points, characters, booleans, etc

## TTK-91 registers

- 8 general registers (for any type of use)

- Only these registers can be directly referenced (with read or write ops) in machine instructions

- All calculations (all work) happen with these registers

- only 8 "memory slots" for actual work

- R0 work register

- If index register Ri==0, it denotes value 0, and not contents of index register Ri, i.e., "no indexing"

- R1-R5 work or index registers

To implement subroutines (<u>not</u> for ordinary computational work) Type depends on where in instr register is used in

work reg 1st operand, index reg in 2nd operand

Stack Pointer SP (i.e., R6)

Frame Pointer FP (i.e., R7)

Stack Pointer

11.3.2020

# TTK-91 Control Unit (CU)

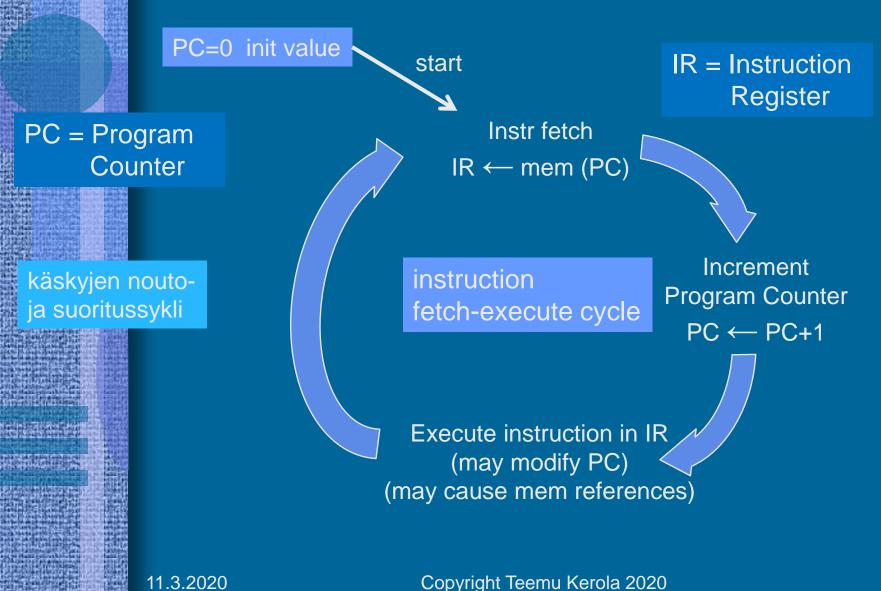

- PC Program Counter (Instruction Pointer, IP)

- Address of <u>next</u> (not current) instruction to execute

- IR Instruction Register

- Current instruction in execution

- TR Temporary Register

- Extra storage for data needed for instruction execution

- SR State Register

- Current processor state and limitations

# TTK-91 State Register SR

- State info on <u>what happened at the processor</u> when this or previous instruction(s) was executed

- Errors, exceptions, interrupts

- Machine instruction was supervisor call (SVC)

- Results of comparisons

- State info on <u>what has happened in the system</u> <u>recently</u>

- Device signals (device interrupts) not yet processed

- State info on what the processor is allowed to do

- Privileged or normal execution state?

- All memory and all instructions allowed, or not?

- Interrupt processing allowed or not?

### Ttk-91 State Register SR (9)

32 bits (each has value 0 or 1)

SR: GEL OZUM IS P D ???????

D = Interrupts Disabled (*kesk. estetty*) P = Privileged mode (*etuoik. tila*) S = SVC (supervisor call) palvelupyyntö I = device Interrupt (*laitekeskeytys*) M = forbidden Memory address U = Unknown instruction Z = divide by ZeroO = arithmetic OverflowGEL = comparison indicators: Greater, Equal, Less

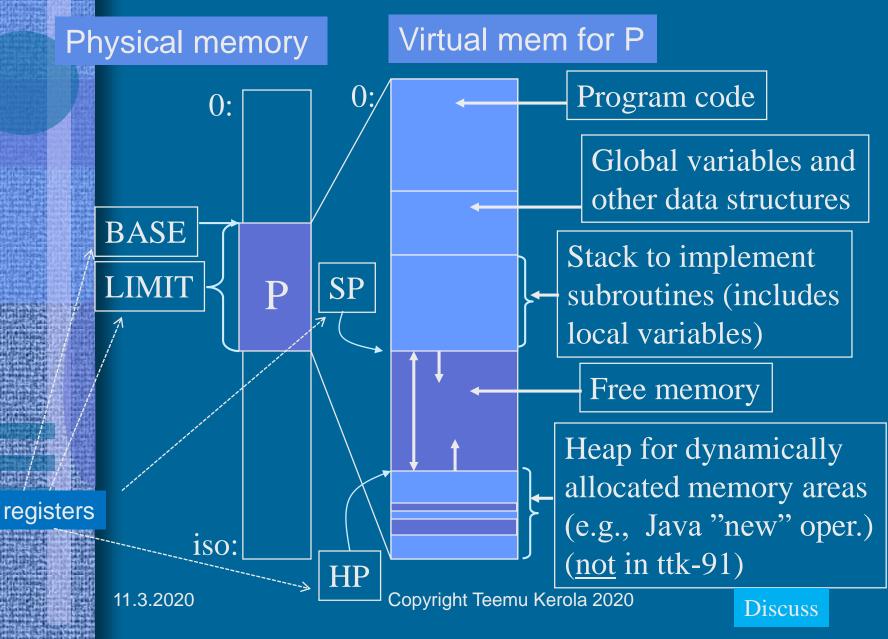

## Memory Use for Program P

12

### Address Translation Mechanisms for Virtual Memory

- Based on base and limit register pairs – ttk-91, 8086, ...

- Paging

- Page tables

- Address space divided into same size "pages"

- Segmenting

- Address space divided into (large?) variable size "segments"

More OS

- Code segment, info? data segment, literal area, heap, stack, ...

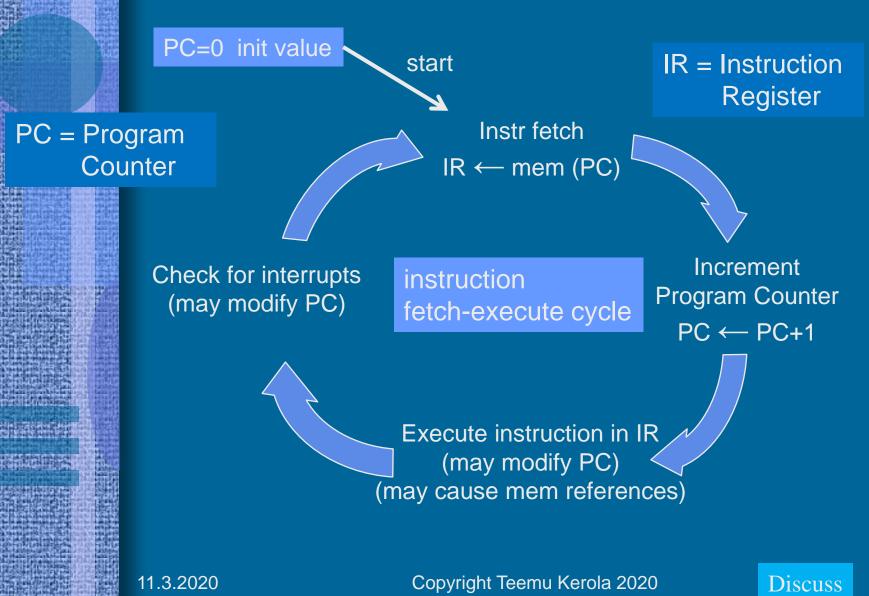

# Interrupt Processing

- Interrupts fetch-execute cycle, "surprise subroutine call", <u>moves control to operating system</u>

- Every possible interrupt type is <u>previously known</u>, i.e., *nothing really surprising does not happen!*

- For each interrupt type there is specific <u>interrupt handler</u> (subroutine) in the operating system

- At the end of every fetch-execute cycle the HW checks for any interrupt existance from SR, and branches to its interrupt handler when needed.

- Old PC and SR saved, new PC and SR set

- E.g., interrupt type 3: PC  $\leftarrow$  3 tai PC  $\leftarrow$  mem(3)

- physical memory address 3?

- Interrupt processing is sometimes <u>disabled</u> (SR bit D in ttk-91)

- Return from interrupt handler with some special instruction (e.g., IRET or "return-from-interrupt-handler")

- Recover old PC and old SR

## **Processor Operation**

## Interrupt Handlers

- Important part of OS (Operating System)

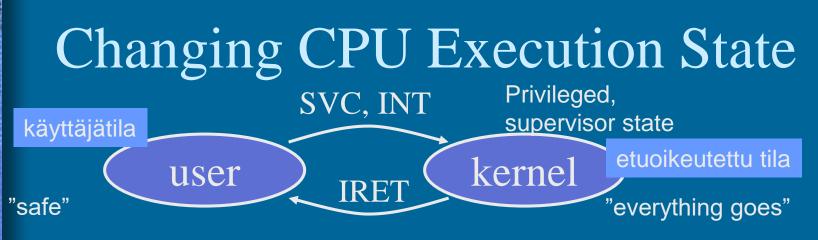

- Before control moves to interrupt handler, processor state is set to <u>privileged state</u> (supervisor state, kernel mode)

- SR bit P is on (1)  $\rightarrow$  processor is in privileged state

- In kernel mode the OS can reference <u>all of memory</u> (MMU: BASE=0, LIMIT="very big")

- In kernel mode the OS can <u>use all instructions</u>

- E.g., IRET, ClearCache, ReadBASE, SetBASE, ReadLIMIT, SetLIMIT, SetD, ResetD, ReadSR, ...

- When returning from interrupt handler processor state is returned back to the one it was originally

- including registers BASE and LIMIT, bit P in SR, etc

- User state  $\rightarrow$  Privileged state

- Interrupt or direct supervisor call (SVC instruction)

- Interrupt handler checks whether state change ok

keskeytyskäsittelijä

- Privileged state  $\rightarrow$  User state

- Privileged machine instruction "return from interrupt handler", e.g., IRET (Pentium II)

- Returns control and processor state to those before control was transferred to interrupt handler

#### Titokone - TTK-91 simulator

- Ordinary program written in Java

- TTK-91 processor/system components as data structures

- registers, MMU, CU, memory

- Simulate fetch-execute cycle, one instr. at a time

- Includes also parts of operating system

- assembler, loader, debugger, interrupt handlers

- Graphical user interface (UI)

See Processor.java in Titokone code:

titokone.jar\fi\hu\cs\titokone\Processor.java

(http://www.cs.helsinki.fi/group/nodes/kurssit/tito/Processor.java.txt)

11.3.2020

### TTK-91 Fetch-execute Cycle

Fetch instruction from simulated memory IR = mem[PC]

Break instr. into fields (OPER, Rj, M, Ri, ADDR) and compute initial address to TR (ADDR tai reg[Ri]+ADDR)  $ADDR = IR \mod 32768$  TR = reg[Ri] + ADDRDo enough memory references (M) to get 2nd operand to register TR TR = mem[TR]

Select proper simulation code based on opcode (OPER) if (opcodeOK[OPER] = FALSE) then SR.U = 1; Simulate instruction execution effects into registers (R0...R7, SR, PC, MAR, MBR) ADD Rj, M ADDR(Ri)  $\Rightarrow$  reg[Rj] += TR; SR.O = ... Stop cycle if SVC or interrupt

Simulator in C: http://www.cs.helsinki.fi/group/nodes/kurssit/tito/simu/simu.c 11.3.2020 Copyright Teemu Kerola 2020

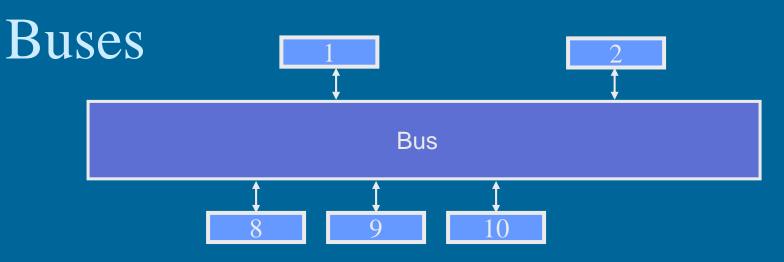

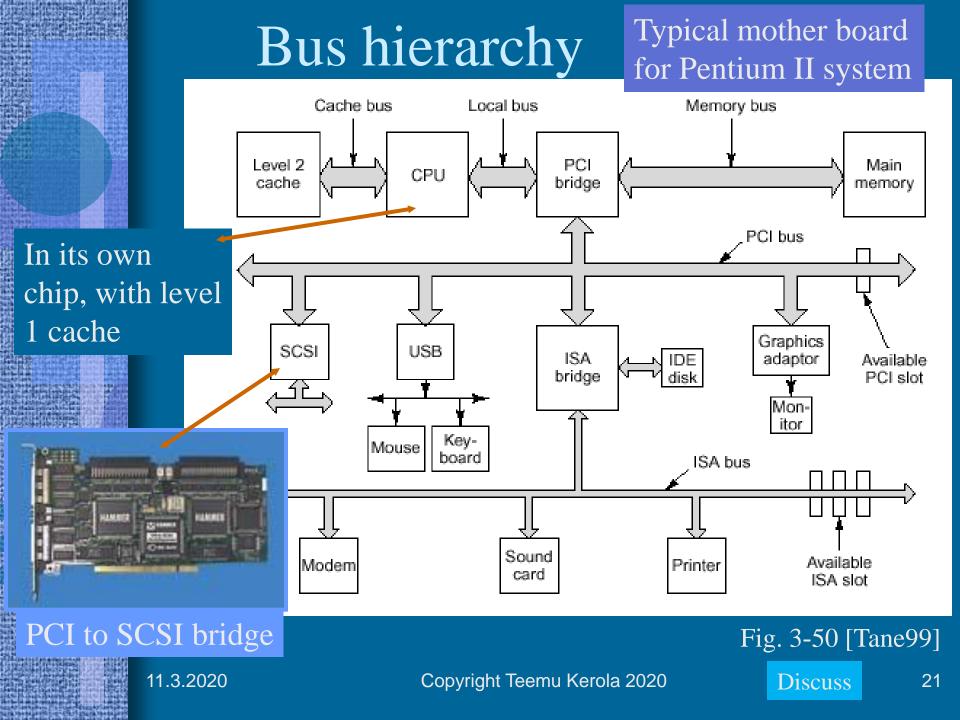

- Each device on the bus has simple address

- One transmits, <u>all</u> listen, only the "correct" device will receive and react to it

- Many different buses, hierarchy of buses

- Those close to CPU are faster

#### -- End --

#### (Tekniikan museo) (The musem of technology)

ESKO, 1960. First "computer" built in Finland, out of date from the start. 20 additions per second. Good learning experience.

- Program code read from paper tape (10 readers)

- Code and data were not in the same memory!

- Subroutine call implemented with control transfer to another tape reader (with subroutine code in looped tape)

11.3.2020