## Instruction Sets Ch 9-10

Characteristics Operands Operations Addressing Instruction Formats

## Instruction Set

#### (käskykanta)

- Collection of instructions that CPU understands

- Only interface to CPU from outside

- CPU executes a program ⇔ CPU executes given instructions "one at a time"

- fetch-execute cycle

## Machine Instruction

• Opcode

- What should I do? Math? Move? Jump?

- Source operand references

- Where is the data to work on? Reg? Memory?

- Result operand reference

- Where should I put the result? Reg? Memory?

- Next instruction reference

- Where is the next instruction? Default? Jump?

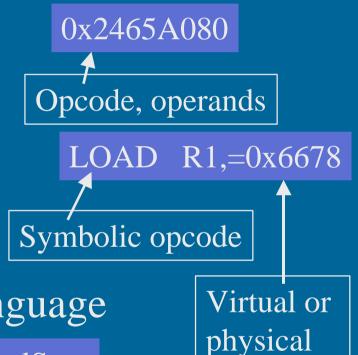

### Instruction Representation

- Bit presentation:

- binary program

- Assembly language

symbolic program

address?

Symbolic assembly language LOAD R1,TotalSum

Fig. 9.11

Symbolic value?

15.11.1999

## Instruction Set Design (5)

- Operation types (operaatiotyyppi)

How many? What type? Simple? Complex?

- Data types

- Just a few? Many?

- Instruction format

(tietotyyppi)

(käskyn muoto)

- fixed length? Varying length? Nr of operands?

- Number of addressable registers

- too many  $\Rightarrow$  long instructions

- Addressing

(tiedon osoitus)

– What modes to use to address data and when?

## Good Instruction Set (2)

- Good target to compiler

- Easy to compile?

- Easy to compile code that runs fast?

- Possible to compile code that runs fast?

- Allows fast execution of programs

- How many meaningless instructions per second?

- How fast does my program run?

- Solve linear system of 1000 variables?

- Set of data base queries?

## Good Instruction Set (contd) (5)

- Beautiful & Aesthetic

- Orthogonal

### (ortogonaalinen)

- Simple, no special registers, no special cases, any data type or addressing mode can be used with any instruction

- Complete

#### (täydellinen)

- Lots of operations, good for all applications

- Regular

#### (säännöllinen)

- Specific instruction field has always same meaning

- Streamlined

- (virtaviivainen)

- Easy to define what resources are used

15.11.1999

## Good Instruction Set (contd) (2)

- Easy to implement

- 18 months vs. 36 months?

- Who will be 1<sup>st</sup> in market? Who will get development monies back and who will not?

- Scalability

#### (skaalautuva)

- Speed up clock speed 10X, does it work?

- Double address length, does design extend?

- E.g., 32 bits  $\Rightarrow$  64 bits  $\Rightarrow$  128 bits?

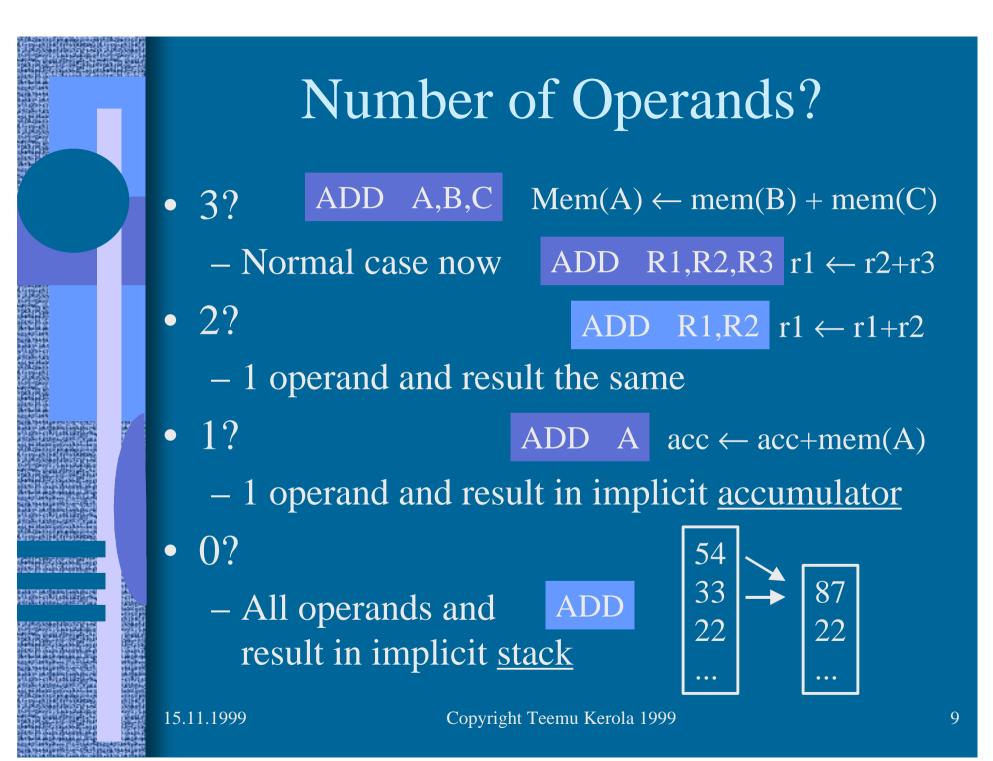

## Instruction Set Architecture (ISA) Basic Classes

- Accumulator

- Stack

- General Purpose Register

- only one type of registers, good for all

- 2 or 3 operands

- Load/Store

- only load/store instructions access memory

- 3 operand ALU instructions

LOAD R3, C LOAD R2,B ADD R1,R2,R3 STORE R1,A

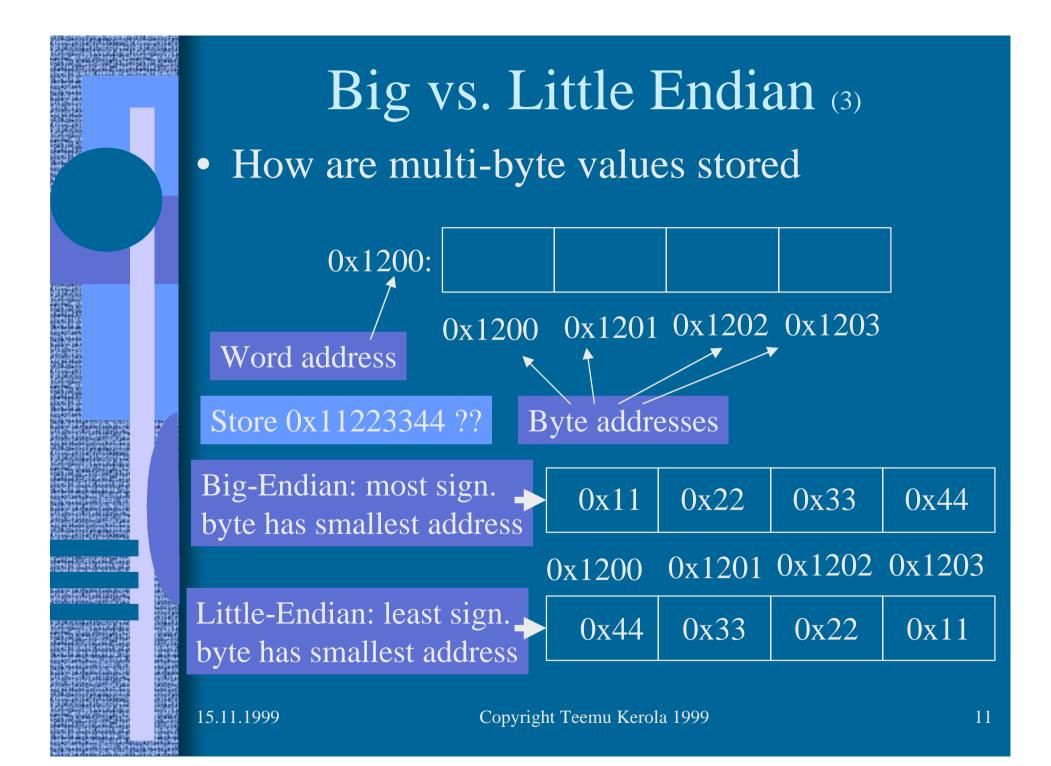

## Big vs. Little Endian

- Address of multi-byte data items is the same in both representations

- Only internal byte order varies

- Must decide one way or the other

- Math circuits must know which presentation used

- Must consider when moving data via network

- Power-PC: bi-endian both modes at use

- can change it per process basis

- kernel mode selected separately

15.11.1999

## Data (Operands, Result) Location

- Register

- close, fast

acc register stack r2, r8

f4, f15

0x345670

- limited number of them

- need to load/store values from/to memory sometimes (often)

- Big problem! 50% of compiler time to decide

- register allocation problem

- Memory

- far away

memory stack (hw regs have mem addresses)

- only possibility for large data sets

- vectors, arrays, sets, tables, objects, ...

15.11.1999

## Aligned Data (4)

2 byte (16-bit) half-word has byte address:

4 byte (32-bit) word has byte address:

8 byte (64-bit) doubleword has byte address:

• Aligned data

44

0010...10010

0010...10100

0010...11000

- faster memory access

- 32-bit data loaded as one memory load

- Non-aligned data

- saves mem, more bus traffic! 33

- 32-bit non-aligned data requires 2 memory loads (each 4 bytes) and combining data into one 32-bit data item

Copyright Teemu Kerola 1999

22

## Data Types (8)

- Address 16b, 32b, 64b, 128b?

- Integer 16b, 32b, 64b?

- Floating point 32b, 64b, 80b?

- Decimal 18 digits (9 bytes) packed decimal?

- Character 1 byte = 8b IRA = ASCII, EBCDIC?

- String finite, arbitrary length?

- Logical data 1 bit (Boolean value, bit field)?

- Vector, array, record, ....

15.11.1999

## Size of Operand

- 1 word, 32 bits

- 2 words, 64 bits

- 4 words, 128 bits

- 1 byte (8 bits) ullet

- 2 bytes

- 1 bit

addr char short int logical values

int, float, addr

double float, addr

## Pentium II Data Types

- General data types

- 8-bit byte

- 16-bit word

- 32-bit doubleword

- 64-bit quadword

- Not aligned

- Big Endian

- Specific data types

- Numerical data types

Table 9.2 Figure 9.4

## **Operation Types**

- Data transfer

- CPU  $\leftrightarrow$  memory

- ALU operations

- INT, FLOAT, BOOLEAN, SHIFT, CONVERSION

- I/O

- read from device, start I/O operation

- Transfer of control

- jump, branch, call, return, IRET, NOP

- System control

- HALT, SYSENTER, SYSEXIT, ...

- CPUID returns current HW configuration

- size of L1 & L2 caches, etc

15.11.1999

Copyright Teemu Kerola 1999

Table 9.3

Table 9.4

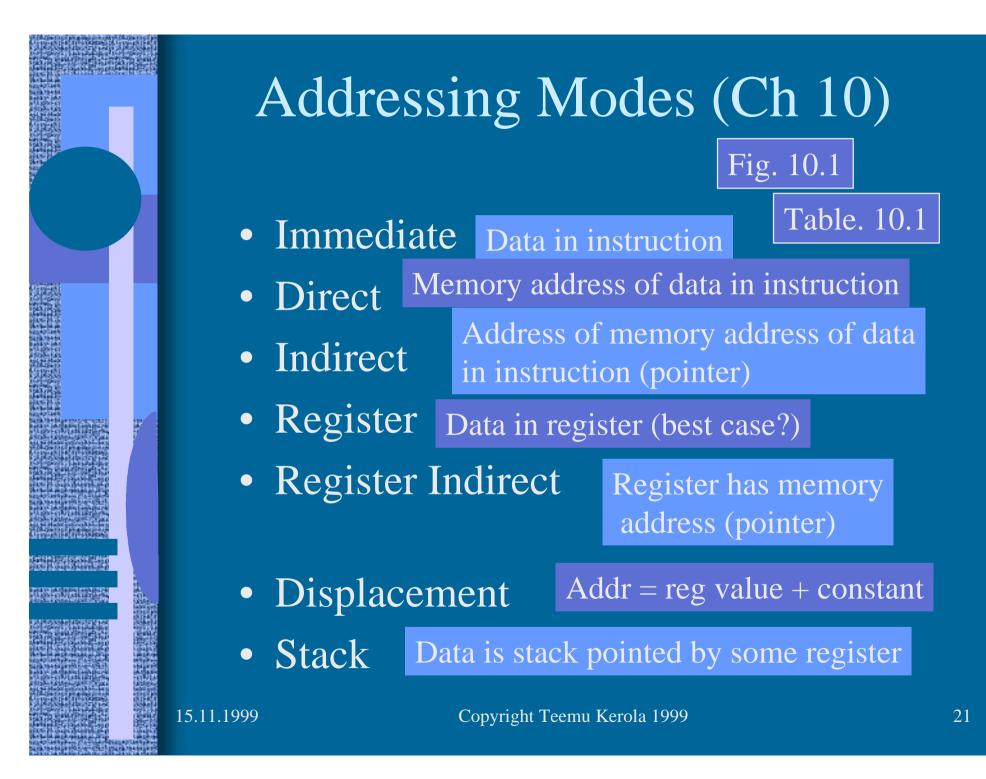

## Data References

- Where is data?

- in memory

- in registers

- in instruction itself

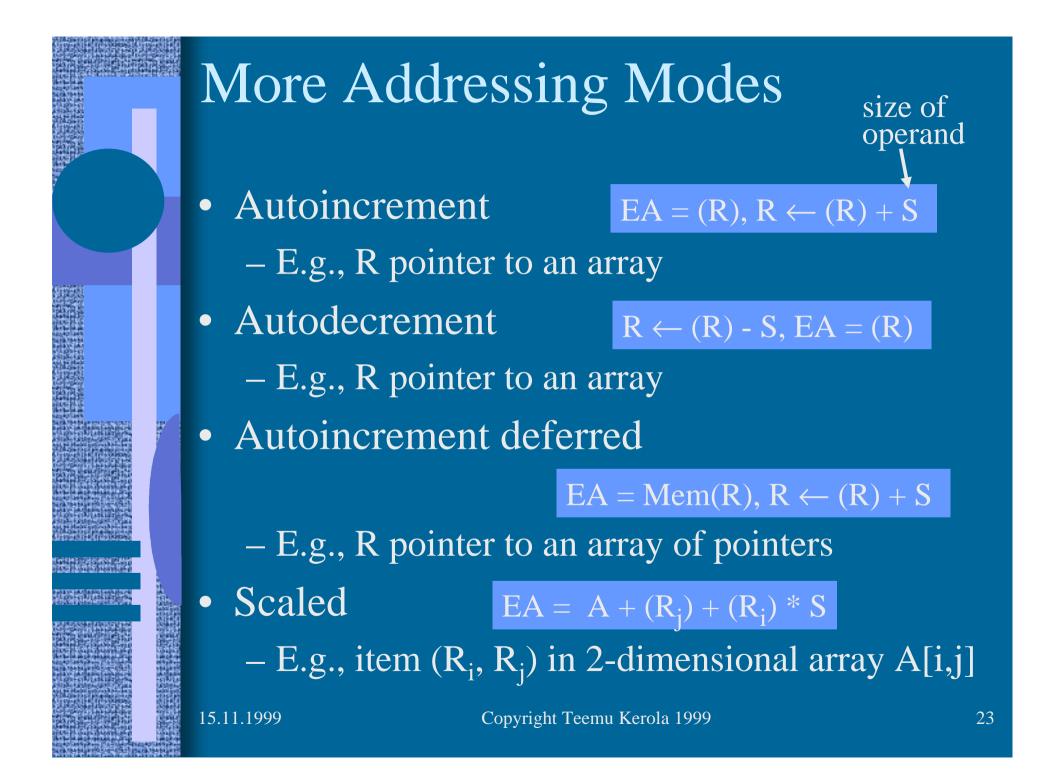

- How to refer to data?

- various addressing modes

- multi-phase data access

- how is data location determined (addressing mode)

- compute data address (register? effective address?)

- access data

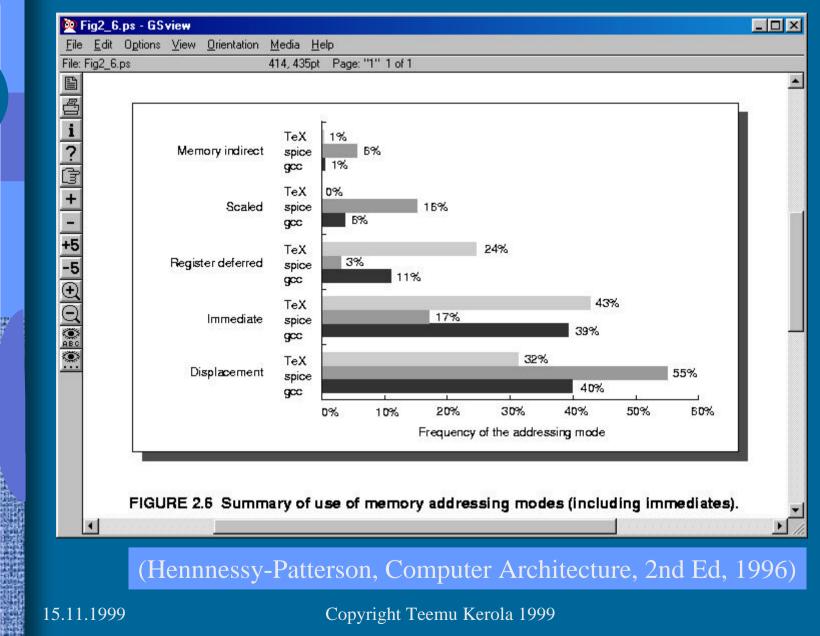

## Pentium II Addressing Modes

• Immediate

15.11.1999

- 1, 2, 4 bytes

- Register operand

- -1, 2, 4, 8 byte registers

- not all registers with every instruction

- Operands in Memory

Fig. 10.2

compute effective address and combine with segment register to get linear address (virtual address)

Table 10.2

## Instruction Format (4)

- How to represent instructions in memory?

- How long instruction

- Descriptive or dense? Code size?

- Fast to load?

- In many parts?

- One operand description at a time?

- Fast to parse?

- All instruction same size & same format?

- Very few formats?

## Instruction Format (contd) (3)

- How many addressing modes?

- Fewer is better, but harder to compile to

- How many operands?

- 3 gives you more flexibility, but takes more space

- How many registers?

- $-16 \text{ regs} \rightarrow \text{need 4 bits to name it}$

- -256 regs  $\rightarrow$  need 8 bits to name it

- need at least 16-32 for easy register allocation

### Instruction Format (contd) (3)

- How many register sets?

- A way to use more registers without forcing long instructions for naming them

- One register set for each subroutine call?

- One for indexing, one for data?

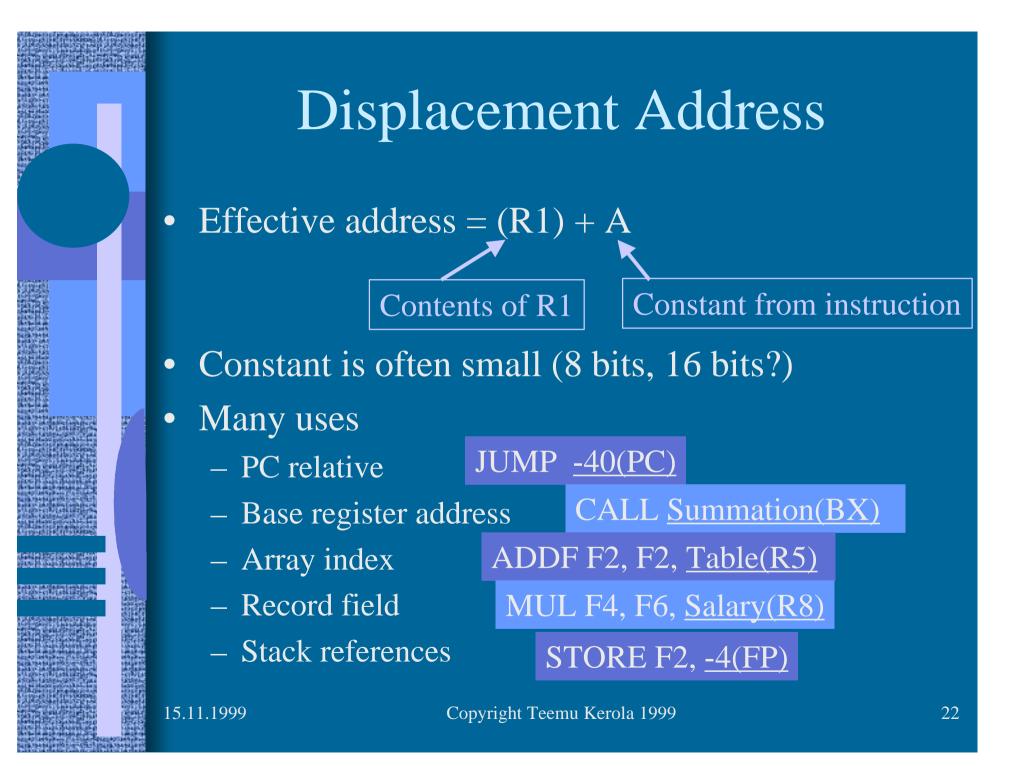

- Address range, number of bits in displacement

- more is better, but it takes space

- Address granularity

- byte is better, but word address is shorter

## Pentium II Instruction Set (5)

- CISC Complex Instruction Set Computer

- At most one memory address

- "Everything" is optional

- "Nothing" is fixed

- Difficult to parse

- all latter fields and their interpretation depends on earlier fields

## Pentium II Instruction Prefix Bytes (4)

Instruction prefix (optional)

- LOCK exclusive use of shared memory

- REP repeat instruction for string characters

- Segment override (optional)

- override default segment register

- default is implicit, no need to store it every instruction

- Address size (optional)

- use the other (16 or 32 bit) address size

- Operand size (optional)

- use the other (16 or 32 bit) operand size

## Pentium II Instruction Fields (3)

- Opcode

- specific bit for byte size data

- Mod r/m (optional)

- data in reg (8) or in mem?

- which addressing mode of 24?

- can also specify opcode further for some opcodes

- SIB (optional)

- extra field needed for some addressing modes

- scale for scaled indexing

- index register

- base register

Fig. 10.8 (b)

# PowerPC Instruction Format (7)

- RISC Reduced Instruction Set Computer

- Fixed length, just a few formats

- Fig. 10.9

- Only load/store instructions access memory

- Only 2 addressing modes for data

- 32 general purpose registers can be used everywhere

- Fixed data size

- no string ops

- Simple branches

- CR-field determines which register to compare

- L-bit determines whether a subroutine call

- A-bit determines if branch is absolute or PC-relative

### -- End of Chapters 9-10: Instruction Sets --