## Hardwired Control Unit Ch 14

Micro-operations Controlling Execution Hardwired Control

11/10/2000

### What is Control (2)

- So far, we have shown what <u>happens</u> inside CPU

- execution of instructions

- opcodes, addressing modes, registers

- I/O & memory interface, interrupts

- Now, we show how CPU <u>controls</u> these things that happen

- how to control what gate or circuit should do at any given time

- control wires transmit control signals

- control unit decides values for those signals

### Micro-operations (2)

#### (mikro-operaatio)

- Basic operations on which more complex instructions are built

Fig. 14.1

- each execution phase (e.g., fetch) consists of one or more sequential micro-ops

- each micro-op executed in <u>one clock cycle</u> in some subsection of the processor circuitry

- each micro-op specifies what happens in some area of cpu circuitry

- cycle time determined by the longest micro-op!

- Micro-ops for (different) instructions can be executed simultaneously

- non-conflicting, independent areas of circuitry

### Instruction Fetch Cycle (10)

- 4 registers involved

- MAR, MBR, PC, IR

- What happens?

Address of next instruction is in PC Address (MAR) is placed on address bus READ command given to memory Result (from memory) appears on data bus Data from data bus copied into MBR PC incremented by 1 New instruction moved from MBR to IR MBR available for new work

#### micro-ops?

$\begin{array}{l} MAR \leftarrow (PC) \\ READ \end{array}$

$MBR \leftarrow (mem)$  $PC \leftarrow (PC) + 1$  $IR \leftarrow (MBR)$

11/10/2000

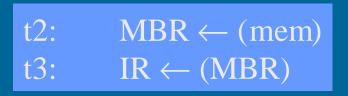

#### Instruction Fetch Micro-ops (3)

- 4 micro-ops

- can not change order

- s2 must be done after s1 s4: IR  $\leftarrow$  (MBR)

- s3 can be done simultanously with s2 implicit

- s4 can be done

with s3, but must

- be done after s2

$\Rightarrow$  Need 3 ticks:

$MAR \leftarrow (PC), READ$  $MBR \leftarrow (mem)$  $PC \leftarrow (PC) + 1$  $IR \leftarrow (MBR)$

s1: MAR  $\leftarrow$  (PC), READ

s2: MBR  $\leftarrow$  (mem)

s3: PC  $\leftarrow$  (PC) +1

Assume: mem read in one cycle

11/10/2000

Copyright Teemu Kerola 2000

t1:

t2:

t3:

## Micro-op Grouping

- Must have proper sequence

- No conflicts

- no write to/read from

with same register

(set?) at the same time

- each circuitry can be used by only one micro-op at a time

- ALU

t1:  $MAR \leftarrow (PC)$ t2:  $MBR \leftarrow (mem)$

$$\begin{array}{ll} 2: & PC \leftarrow (PC) + 1 \\ 3: & R1 \leftarrow (R1) + (MBR) \end{array}$$

## Micro-op Types (4)

- Transfer data from one reg to another

- Transfer data from reg to external area

- memory

- I/O

- Transfer data from external to register

- ALU or logical operation between registers

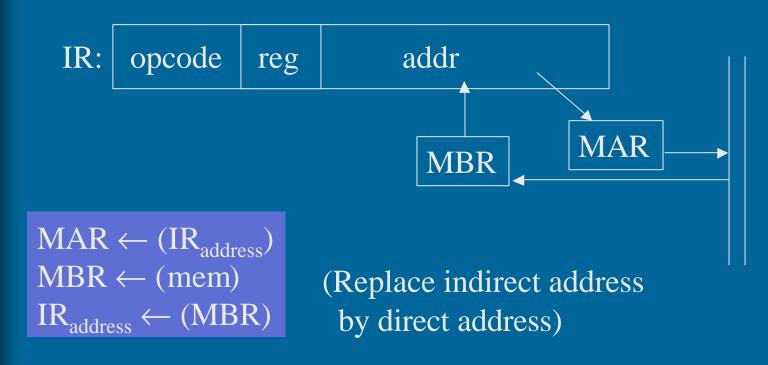

## Indirect Cycle

• Instruction contains indirect address of an operand, instead of direct operand address

11/10/2000

## Interrupt Cycle

- After execution cycle test for interrupts

- If interrupt bits on, then

- save PC to memory

- jump to interrupt handler

- t1:  $MBR \leftarrow (PC)$

- t2: MAR  $\leftarrow$  save-address PC  $\leftarrow$  routine-address t3:  $\frown$  mem  $\leftarrow$  (MBR)

- or, find out first correct handler for this type of interrupt and then jump to that (need more micro-ops)

context saved by interrupt handler

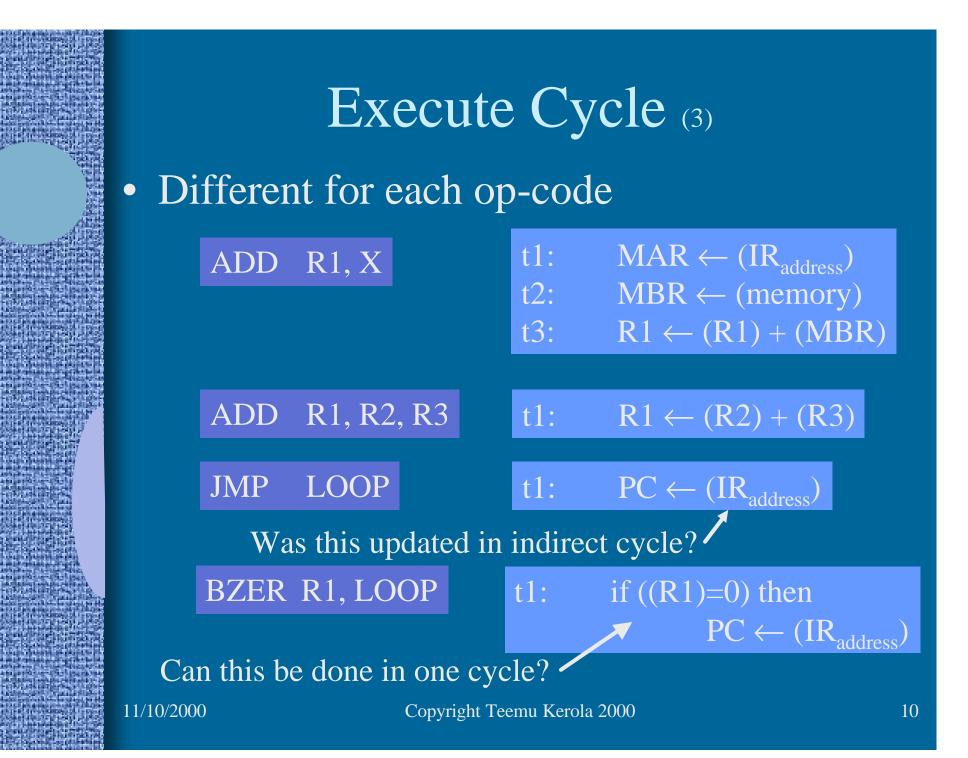

#### Execute Cycle (contd) (1)

BSA MySub

#### MySub: DC LOAD ...

t1: MAR  $\leftarrow$  (IR<sub>address</sub>) MBR  $\leftarrow$  (PC) t2: PC  $\leftarrow$  (IR<sub>address</sub>) memory  $\leftarrow$  (MBR) t3: PC  $\leftarrow$  (PC) + 1

Return address stored here

**RET MySub**

1<sup>st</sup> instruction in MySub+1

11/10/2000

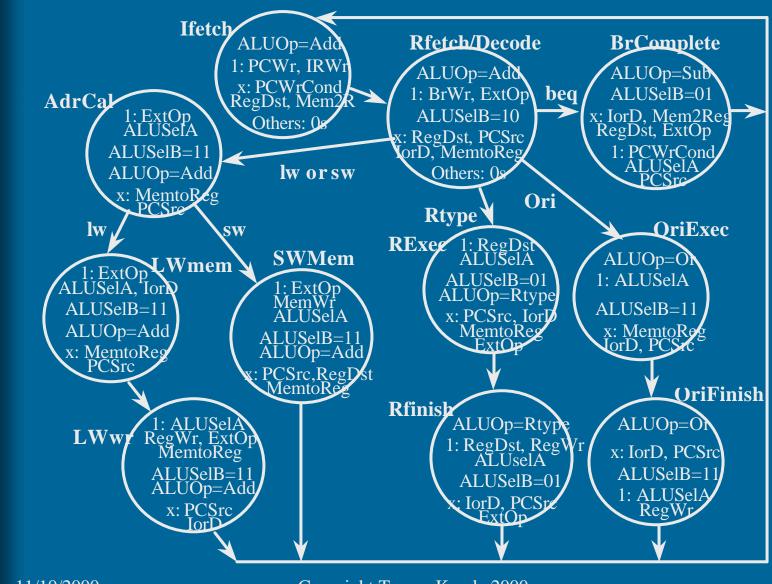

## Instruction Cycle (3)

- Decomposed to micro-ops

- State machine for processor

- state: execution phase

- sub-state: current group of micro-ops

- In each sub-state the control signals have specific values dependent

- on that sub-state

- on IR register fields and flags

- including control signals from the bus

- including values (flags) produced by previous substate

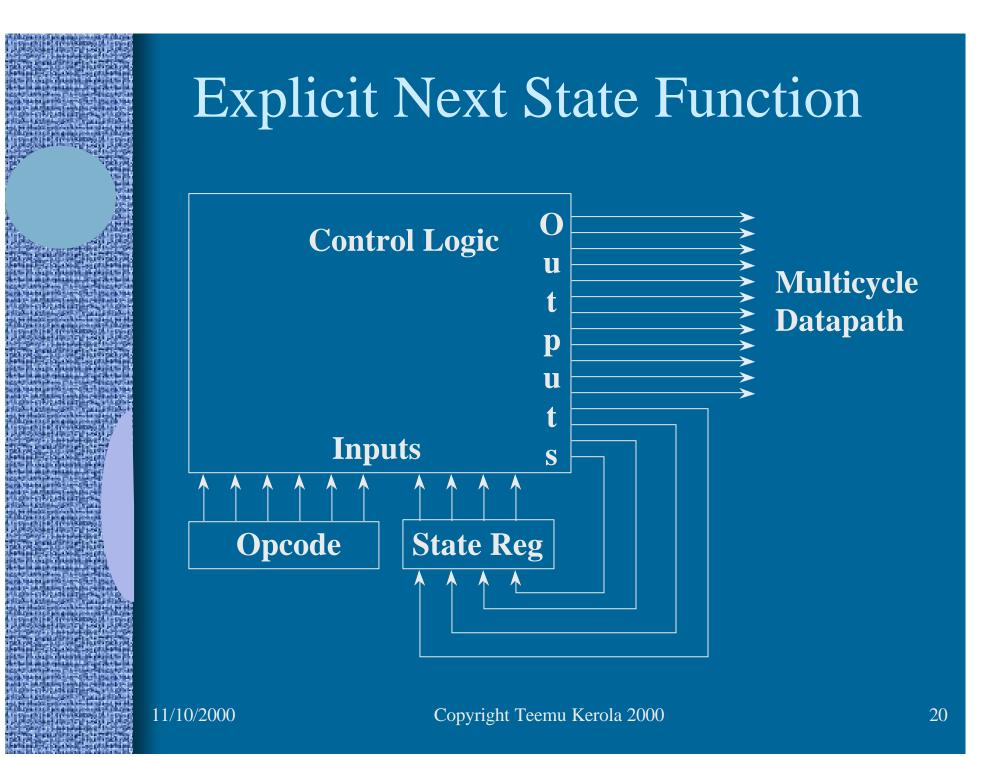

### Control State Machine (2)

- Each state defines current control signal values

Control execution

- determines what happens in next clock cycle

Current state and current register/flag values determine next state

Control sequencing

# Control Signal Types (3)

- Control data flow from one register to another

- Control signals to ALU

- ALU does also all logical ops

- Control signals to memory or I/O devices

via control bus

## Control Signal Example (4)

• Accumulator architecture

- Control signals for given micro-ops

<u>cause</u> micro-ops to be executed Table 14.1

- setting C<sub>2</sub> makes value stored in PC to be copied to MAR in next clock cycle

- C<sub>2</sub> controls Input Data Strobe for MAR (see Fig. A.30 for register circuit)

- setting C<sub>R</sub> & C<sub>5</sub> makes memory perform

a READ and value in data bus copied to

MBR in next clock cycle

11/10/2000

#### Example: Intel 8085 (5) Introduced 1976 • <u>3, 5, or 6 MHz, no cache</u> • 8 bit data bus, 16 bit address bus – multiplexed • One 8-bit accumulator opcode address LDA MyNumber 0x3A 0x10A5 3 bytes 0x02 0x2B2 bytes OUT #2 opcode port

## Example: i8085 (6)

- Instead of complex data path all data transfers within CPU go via internal bus

Fig. 14.7

- may not be good approach for superscalar pipelined processor - bus should not be bottleneck

- External signals

Table 14.2

- Each instruction is 1-5 <u>machine cycles</u>

- one external bus access per machine cycle

- Each machine cycle is 3-5 states

- Each state is one clock cycle

- Example: OUT instruction

Fig. 14.9

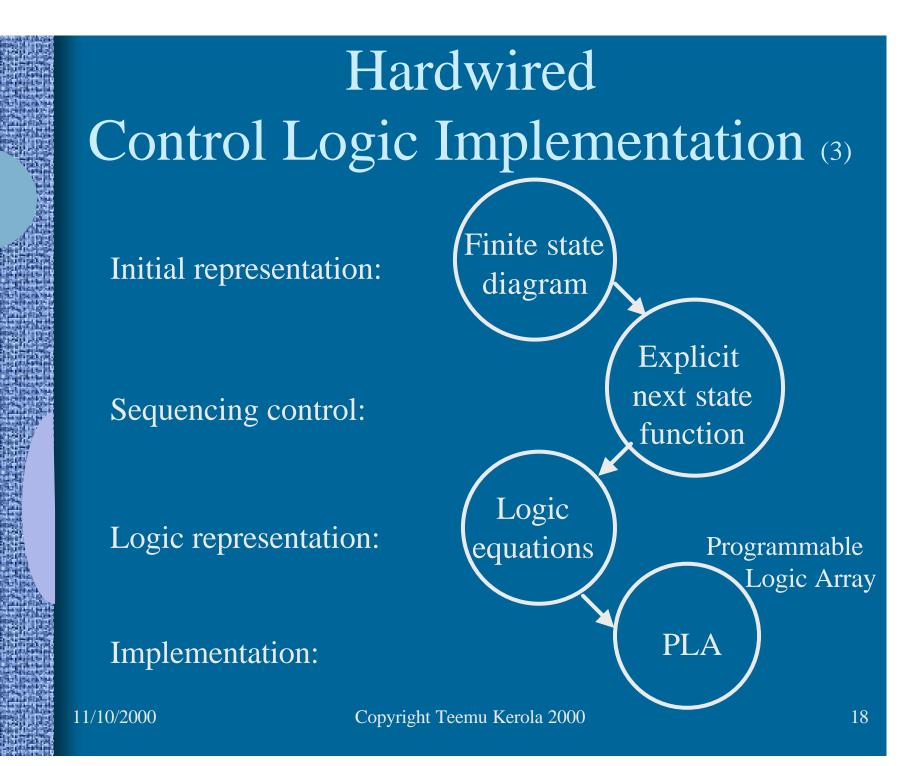

### Finite State Diagram

11/10/2000

## Logic Equations

#### Next state from current state

- -State 0 -> <u>State1</u>

- State 1 -> S2, S6, S8, S10

- State 2 ->\_\_\_\_\_

- State 3 ->\_\_\_\_

- State 4 -> <u>State 0</u>

- State 5 -> <u>State 0</u>

- State 6 -> <u>State 7</u>

- -State 7 -> <u>State 0</u>

- -State 8 -> <u>State 0</u>

- State 9-> <u>State 0</u>

- State 10 -> <u>State 11</u>

- State 11 -> <u>State 0</u>

Alternatively, prior state & condition

- <u>S4, S5, S7, S8, S9, S11</u> -> State0

- -> State1

- \_\_\_\_- -> State 2

- \_\_\_\_\_ -> State 3

- \_\_\_\_\_ -> State 4

- State2 & op = SW -> State 5

- \_ -> State 6

- State 6 -> State 7

- \_\_\_\_\_ -> State 8

- State2 & op = JMP -> State 9

- \_\_\_\_ -> State 10

- State 10 -> State 11

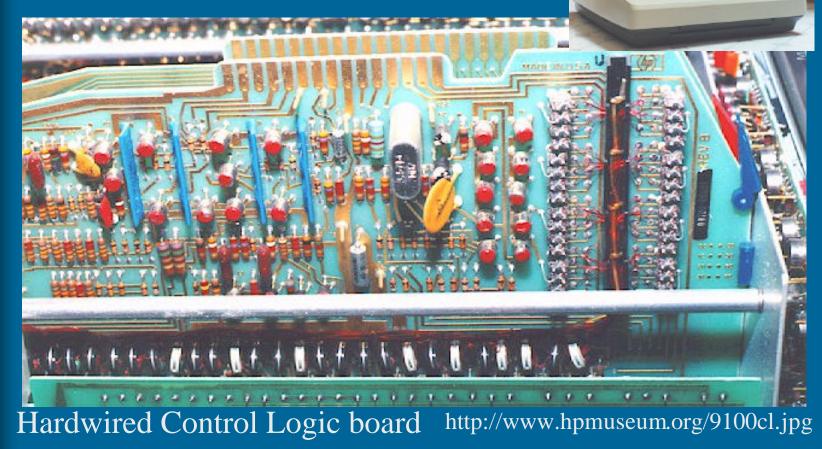

## Hardwired Control Logic (3)

- Circuitry becomes very big and complex very soon

- may be unnecessarily slow

- simpler is smaller, and thus faster

- Many lines (states) exactly or almost similar

- Have methods to find similar lines and combine them

- not simple

- save space, may lose in speed

#### -- End of Chapter 14: Hardwired Control --

HP 9100 Calculator (1968), 20 kg, \$5000, 16 regs (data or 14 instructions/reg), 32Kb ROM, 2208 bit RAM magnetic core memory

11/10/2000