#### RISC Architecture Ch 12

Instruction Usage

Characteristics

Large Register Files

Register Allocation

Optimization

RISC vs. CISC

- General purpose computer

- Howard Aiken, Mark I, 1944

- relays, 17m long, 2.4m tall

- 500 miles of wire, 5 tons

- 3 million connections

- 6 sec mult, 12 sec div

- IBM ASCC (automatic sequence controlled calculator)

- turned off last time 1959

Copyright (c) 1997.

Maxfield & Montrose Interactive Inc

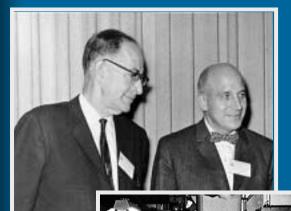

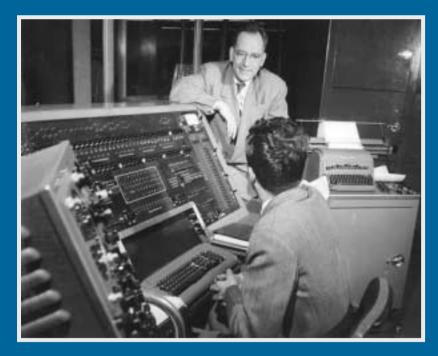

J. P. Eckert and John

Mauchly, Eniac, 1946

- 1500 relays

- 18000 vacuum tubes

- 70,000 resistors

- 20 accumulators

- 10 digits

- modify program by rewiring

- Stored Program Computer

- store both program and data in memory

- John von Neumann, 1945

- Electronic Discrete

Variable Automatic

Computer (EDVAC) prototype

- Maurice Wilkes, 1949

- Electronic Delay Storage Automatic Calculator (EDSAC)

- first fully operational stored program computer

- software was born

- Floating Point hardware

- Gene Amdahl, 1953

- IBM 704

- OS allowed for batch processing

- combine existing commands into new commands

- 5 kFLOPS

- 19 units produced

- Family of computers with different implementations of the same architecture

- Computer system can grow within the family and all SW will still run

- Need faster/bigger⇒ buy a faster/biggersystem in the family

- Gene Amdahl

- IBM S/360

- DEC PDP-8

- Microprogrammed control unit

- can modify implementation easily

- makes it easier to implement families of systems

- can have different instruction set architecture

(ISA) on top of the same HW

- Maurice Wilkes, 1951

- IBM System/360,1964

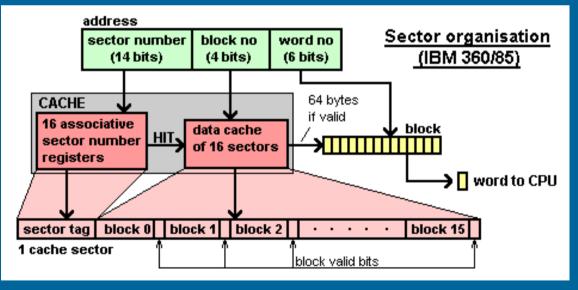

- Cache memory

- Maurice Wilkes, 1965

- major speed up

- IBM System/360

Model 85

1968

- Tom Kilburn, 1962

- Atlas, 1962

- 20 bits for virtual address space

- 512 word (each48 bits) page

- 16 KB main mem

- 2 units sold

Atlas accumulator cabinet

- Pipelining

- Tom Kilburn (?)

- Atlas, 1962

- 2 ALU's

- overlap execution of 3 instructions

Atlas Main and B-Arithmetic Units

- Multiple processors

- J. P. Eckert and John Mauchly

- Sperry Rand Univac1108II (1108A), 1964

- 3 CPU's

- 2 I/O controllers

- DMA

- 36 bit words

- test-and-set instruction was added for synchronization between processors

Mauchly & Univac console

- Static RAM

- Fairchild 4100, 1970

- 256 bits

- Dynamic Random Access Memory

- Robert Dennard, IBM, 1966

- Intel 1103, 1970

- John Reed

- 1024 bits

- replaces magnetic core memory by 1972

Dennard

Reed

#### Major Inventions in Computer

Architecture

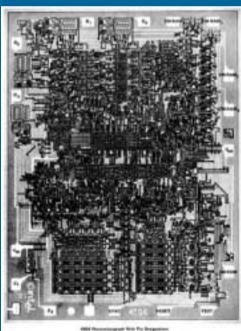

- Single chip microprocessor

- Marcian E. (Ted) Hoff,(+ Federico Faggin& Stan Mazor ?)

- Intel 4004, 1971

Mazor

- 2250 transistors, 60K OPS

- "single chip which implements and interprets all microinstructions"

- 4 bit words, 16 GPRs, 4-bit accumulator, operation register, instruction decoder

- good for BCD operations (BCD = Binary Coded Decimal)

- Japanese investors (Busicom) abandoned failed (!) project

- Vector processors

- operate on entire vectors with one instruction

- Texas Instrument Advanced Scientific Computer

(ASC), 1971

- W. Joe Watson

- 4 pipelines

- vectors stored in memory

- 7 machines built

- vectorizing Fortran compiler

- theoretical max speed 50 MFLOPS

- slow scalar unit

• ... ??? ...

#### Major Inventions in Computer Architecture (2) • Reduced Instruction Set Computer (RISC) – John Cocke, 1974 - IBM 801 (prototype), 1979 project cancelled because

- instruction set not compatible with OS/360

- Try again ... and succeed

- Hennessy (1981) & Patterson (1980)

- Proved, that even CISC machines may work faster if only simple instructions and addressing modes are used

- Make cache visible to application and (partly) under application control

- Edmund J. Kelly, Malcolm John Wing

& Robert Cmelik, Transmeta Corp., 1996

- Certain applications can optimize and dynamically rebuild (translate & optimize) their (instruction) cache

- lots of work, possibly big speedups

- E.g., emulators for other architectures

- Crusoe processor, 2000