# Hardwired Control Unit Ch 14

Micro-operations Controlling Execution Hardwired Control

10/10/2001

Copyright Teemu Kerola 2001

#### Instruction Fetch Cycle (10) • 4 registers involved Fig. 11.7 - MAR, MBR, PC, IR • What happens? micro-ops? Address of next instruction is in PC $MAR \leftarrow (PC)$ Address (MAR) is placed on address bus READ command given to memory READ Result (from memory) appears on data bus Data from data bus copied into MBR $MBR \leftarrow (mem)$ $PC \leftarrow (PC) + 1$ PC incremented by 1 $IR \leftarrow (MBR)$ New instruction moved from MBR to IR MBR available for new work Copyright Teemu Kerola 2001

#### What is Control (2)

- So far, we have shown what <u>happens</u> inside CPU

- execution of instructions

- · opcodes, addressing modes, registers

- I/O & memory interface, interrupts

- Now, we show how CPU <u>controls</u> these things that happen

- how to control what gate or circuit should do at any given time

- · control wires transmit control signals

Copyright Teemu Kerola 200

· control unit decides values for those signals

10/10/2001

Instruction Fetch Micro-ops (3) s1: MAR  $\leftarrow$  (PC), READ • 4 micro-ops s2: MBR  $\leftarrow$  (mem) can not change order s3:  $PC \leftarrow (PC) + 1$ - s2 must be done after s1 s4: IR ← (MBR) - s3 can be done simultaneously with s2 implicit - s4 can be done with s3, but must  $MAR \leftarrow (PC), READ$ be done after s2 t2:  $MBR \leftarrow (mem)$  $PC \leftarrow (PC) + 1$ ⇒ Need 3 ticks: t3:  $IR \leftarrow (MBR)$ Assume: mem read in one cycle Copyright Teemu Kerola 200

### Micro-operations (2)

(mikro-operaatio)

- Basic operations on which more complex instructions are built

Fig. 14.1

- each execution phase (e.g., fetch) consists of one or more sequential micro-ops

- each micro-op executed in <u>one clock cycle</u> in some subsection of the processor circuitry

- each micro-op specifies what happens in some area of cpu circuitry

- cycle time determined by the longest micro-op!

- Micro-ops for (different) instructions can be executed simultaneously

- non-conflicting, independent areas of circuitry

0/10/2001 Copyright Teemu Kerola 2001

# Micro-op Grouping

- Must have proper sequence

- t1:  $MAR \leftarrow (PC)$ t2:  $MBR \leftarrow (mem)$

- · No conflicts

- no write to/read from with same register (set?) at the same time

t2:  $MBR \leftarrow (mem)$ t3:  $IR \leftarrow (MBR)$

- each circuitry can be used by only one micro-op at a time

- t2:  $PC \leftarrow (PC) + 1$ t3:  $R1 \leftarrow (R1) + (MBR)$

- E.g., ALU

0/10/2001 Copyright Teemu Kerola 2001

# Micro-op Types (4)

- Transfer data from one reg to another

- Transfer data from reg to external area

- memory

- I/O

- · Transfer data from external to register

- ALU or logical operation between registers

10/10/2001 Copyright Teemu Kerola 2001 7

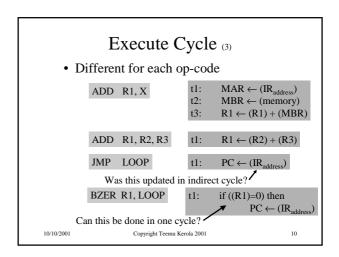

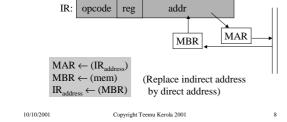

# Indirect Cycle • Instruction contains indirect address of an operand, instead of direct operand address IR: Opcode reg addr

# Interrupt Cycle

- After execution cycle test for interrupts

- If interrupt bits on, then

- save PC to memory

- jump to interrupt handler

- or, find out first correct handler for this type of interrupt

- and then jump to that (need more micro-ops)

t1:

t2:

t3:

$MBR \leftarrow (PC)$

$\text{mem} \leftarrow (\text{MBR})$

$MAR \leftarrow save\text{-}address$

$PC \leftarrow routine\text{-}address$

implicit - just wait?

- context saved by interrupt handler

10/10/2001 Copyright Teemu Kerola 2001

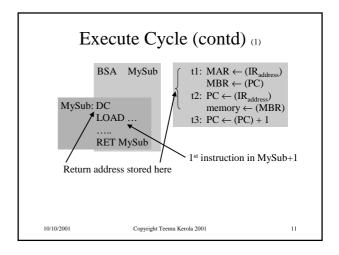

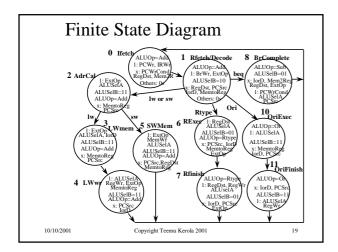

# Instruction Cycle (3)

- Decomposed to micro-ops

- · State machine for processor

- state: execution phase

- sub-state: current group of micro-ops

- In each sub-state the control signals have specific values dependent

Fig. 14.3

Fig. 14.4

- on that sub-state

- on IR register fields and flags

- including control signals from the bus

- including values (flags) produced by previous sub-state

0/10/2001 Copyright Teemu Kerola 2001 12

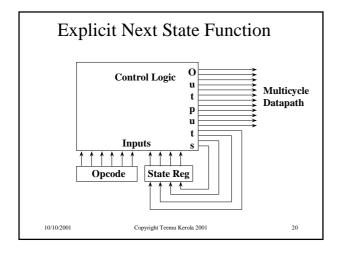

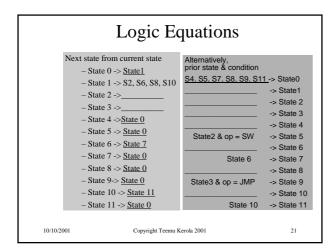

#### Control State Machine (2)

- Each state defines current control signal values Control execution

- determines what happens in next clock cycle

- Current state and current register/flag values determine next state

Control sequencing

10/10/2001

Copyright Teemu Kerola 2001

# Example: Intel 8085 (5) Introduced 1976 3, 5, or 6 MHz, no cache 8 bit data bus, 16 bit address bus - multiplexed One 8-bit accumulator LDA MyNumber opcode address Ox3A Ox10A5 3 bytes OUT #2 Ox2B Ox02 opcode port

### Control Signal Types (3)

- Control data flow from one register to another

- Control signals to ALU

- ALU does also all logical ops

- Control signals to memory or I/O devices

- via control bus

10/10/2001

Copyright Teemu Kerola 2001

# Example: i8085 (6)

Copyright Teemu Kerola 2001

- Instead of complex data path all data transfers within CPU go via internal bus Fig. 14.7

- may not be good approach for superscalar pipelined processor - bus should not be bottleneck

- · External signals

10/10/2001

Table 14.2

- Each instruction is 1-5 <u>machine cycles</u>

- $\,-\,$  one external bus access per machine cycle

- Each machine cycle is 3-5 states

- · Each state is one clock cycle

- Example: OUT instruction

Fig. 14.9

10/10/2001 Copyright Teemu Kerola 2001

# Control Signal Example (4)

Accumulator architecture

Fig. 14.5

14

Control signals for given micro-ops cause micro-ops to be executed

Table 14.1

- setting C<sub>2</sub> makes value stored in PC to be copied to MAR in next clock cycle

- C<sub>2</sub> controls Input Data Strobe for MAR (see Fig. A.30 for register circuit)

- setting C<sub>R</sub> & C<sub>5</sub> makes memory perform a READ and value in data bus copied to MBR in next clock cycle

10/10/2001

Copyright Teemu Kerola 2001

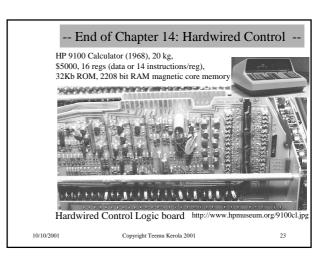

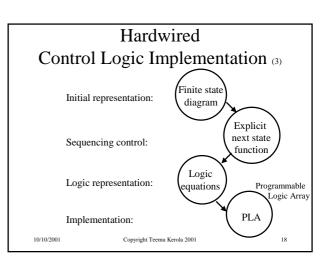

# Hardwired Control Logic (3)

- Circuitry becomes very big and complex very soon

- may be unnecessarily slow

- simpler is smaller, and thus faster

- Many lines (states) exactly or almost similar

- Have methods to find similar lines (states) and combine them

- not simple

- save space, may lose in speed

10/10/2001 Copyright Teemu Kerola 2001 22