| 10/10/2001 | Copyright Teemu Kerola 2001 | 24 |

|------------|-----------------------------|----|

## Summary (10)

- How clock signals cause instruction executions?

- Low level stuff

- gates, basic circuits, registers, memory

- Cache

- Virtual memory & TLB

- ALU, int & FP arithmetic's

- Instruction sets

- CPU structure & pipelining

- Branch prediction, limitations, hazards, issue

- RISC & superscalar processor

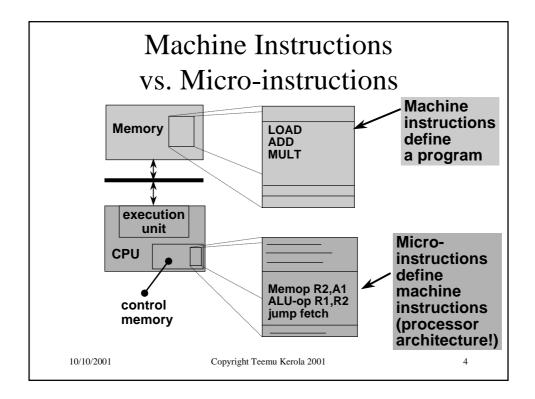

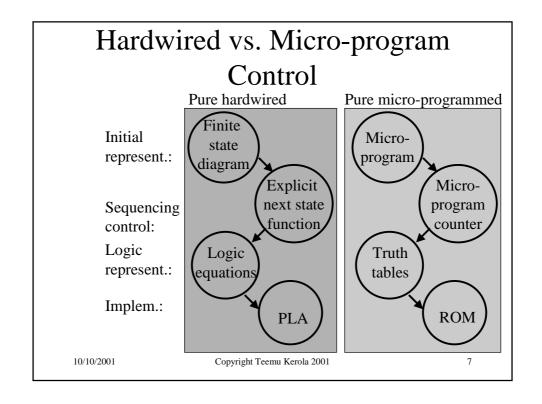

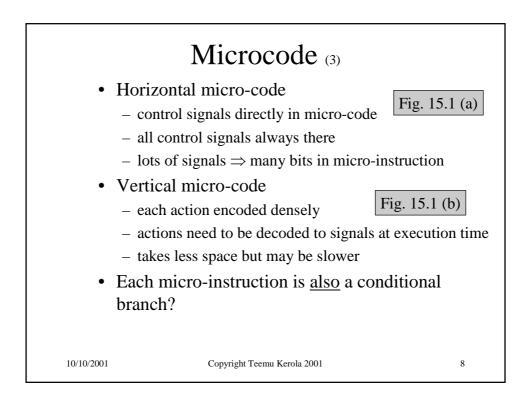

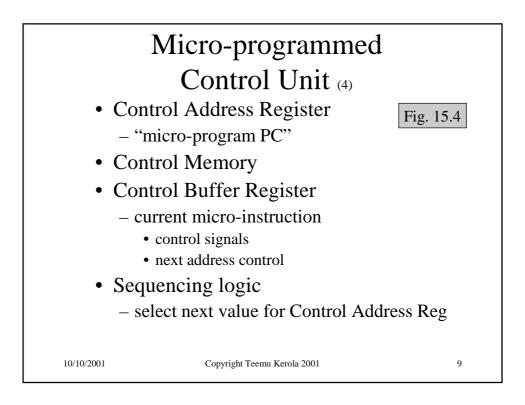

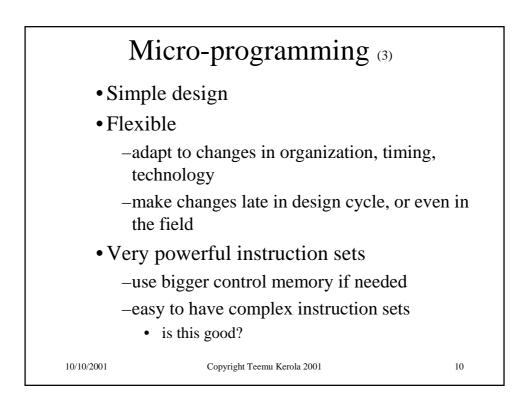

- Hardwired & micro-controlled control

10/10/2001

Copyright Teemu Kerola 2001