## Memory Hierarchy and Cache Ch 4.1-3

Memory Hierarchy

Main Memory

Cache

Implementation

19/09/2001

Copyright Teemu Kerola 2001

#### Teemu's Cheesecake Register, on-chip cache, memory, disk, and tape speeds relative to times locating cheese for the cheese cake you are baking... Europa refridge-(Jupiter) rator hand moon 1 sec 10 sec 0.5 sec (cache) 12 days 4 years (register) (memory) (disk) (tape) 19/09/2001 Copyright Teemu Kerola 2001

## Goal (4)

- I want my memory lightning fast

- I want my memory to be gigantic in size

- Register access viewpoint:

- data access as fast as from HW register

- data size as large as memory

HW solution

- Memory access viewpoint

- data access as fast as from memory

- virtual memory

data size as large as disk

HW help for SW solution

19/09/2001

Copyright Teemu Kerola 2001

## Memory Hierarchy (5)

- Most often needed data is kept close

- Access to small data sets can be made fast

- simpler circuits

- Faster is more expensive

- Large can be bigger and cheaper

Memory Hierarchy

Fig. 4.1

up: smaller, faster, more expensive,

more frequent access

down: bigger, slower, less expensive,

less frequent access

19/09/2001

Copyright Teemu Kerola 2001

## Principle of locality (7)

(paikallisuus)

- In any given time period, memory references occur only to a <u>small subset</u> of the whole address space

- The reason why memory hierarchies work

- Average cost is close to the cost of small data set

- How to determine that small data set?

- How to keep track of it?

19/09/2001

Copyright Teemu Kerola 2001

5

# Principle of locality (5)

- In any given time period, memory references occur only to a <u>small subset</u> of the whole address space (paikallisuus)

- <u>Temporal locality</u>: it is likely that a data item referenced a short time ago will be referenced again soon (ajallinen paikallisuus)

- <u>Spatial locality:</u> it is likely that a data items close to the one referenced a short time ago will be referenced soon (alueellinen paikallisuus)

19/09/2001

Copyright Teemu Kerola 2001

#### Memory

- Random access semiconductor memory

- give address & control, read/write data

- ROM, PROMS

Table 4.2

- system startup memory,BIOS (Basic Input/Output System)

- load and execute OS at boot

- also random access

- RAM

- "normal" memory accessible by CPU

19/09/2001

Copyright Teemu Kerola 2001

7

#### **RAM**

E.g., \$0.12 / MB (year 2001)?

- Dynamic RAM, DRAM

- simpler, slower, denser, bigger (bytes per chip)

- main memory?

E.g., 60 ns access

- periodic refreshing required

- refresh required after read

- Static RAM, SRAM E.g., \$0.50 / MB (year 2001)?

- more complex (more chip area/byte), faster,

smaller (bytes per chip)

- cache?

E.g., 5 ns access?

- no periodic refreshing needed

- data remains until power is lost

19/09/2001

Copyright Teemu Kerola 2001

#### **DRAM Access**

- 16 Mb DRAM

- 4 bit data items

Fig. 4.4

Fig. 4.5 (b)

- 4M data elements, 2K \* 2K square

- Address 22 bits

- row access select (RAS)

- column access select (CAS)

- interleaved on 11 address pins

- Simultaneous access to many 16Mb memory chips to access larger data items

- Access 32 bit words in parallel? Need 8 chips.

19/09/2001

Copyright Teemu Kerola 2001

(

## SDRAM (Synchronous DRAM)

- 16 bits in parallel

- access 4 SDRAMs in parallel

- Faster than plain DRAM

- Current main memory technology (year 2001)

E.g., \$0.11 / MB (year 2001)

19/09/2001

Copyright Teemu Kerola 2001

#### RDRAM (RambusDRAM)

- New technology, works with fast memory bus

- expensive

E.g., \$0.40 / MB (year 2001)?

• Faster transfer rate than with SDRAM

E.g., 1.6 GB/sec vs. 200 MB/sec (?)

• Faster access than SDRAM

E.g., 38 ns vs. 44 ns

- Fast internal Rambus channel (800 MHz)

- Rambus memory controller connects to bus

- Speed slows down with many memory modules

- serially connected on Rambus channel

- not good for servers with 1 GB memory (for now!)

- 5% of memory chips (year 2000)

19/09/2001

Copyright Teemu Kerola 2001

11

19/09/2001 Copyright Teemu Kerola 2001 12

#### Cache Memory

(välimuisti)

- Problem: how can I make my (main) memory as fast as my registers?

- Answer: (processor) cache

- keep most probably referenced data in fast cache close to processor, and rest of it in memory

- much smaller than main memory

- (much) more expensive (per byte) than memory

- most of data accesses to cache

90% 99%?

Fig. 4.13

Fig. 4.16

19/09/2001

Copyright Teemu Kerola 2001

13

## Memory references with cache (5)

• Data is in cache?

Hit

Fig. 4.15

Data is only in memory?

Read it to cache

CPU waits until data available

Miss

Many blocks (cache lines) help for temporal locality many different data items in cache

Fig. 4.14

<u>Large</u> blocks help for <u>spatial</u> locality lots of "nearby" data available

Fixed cache size?

Select "many" or "large"?

19/09/2001

Copyright Teemu Kerola 2001

#### Cache Features (6)

- Size

- Mapping function

(kuvausfunktio)

- how to find data in cache?

- Replacement algorithm

(poistoalgoritmi)

- which block to remove to make room for a new block?

- Write policy

(kirjoituspolitiikka)

- how to handle writes?

- Line size (block size)?

(rivin tai lohkon koko)

• Number of caches?

19/09/2001

Copyright Teemu Kerola 2001

15

#### Cache Size

- Bigger is better in general

- Bigger may be slower

- lots of gates, cumulative gate delay?

- Too big might be too slow!

- Help: 2- or 3-level caches

1KW (4 KB), 512KW (2 MB)?

19/09/2001

Copyright Teemu Kerola 2001

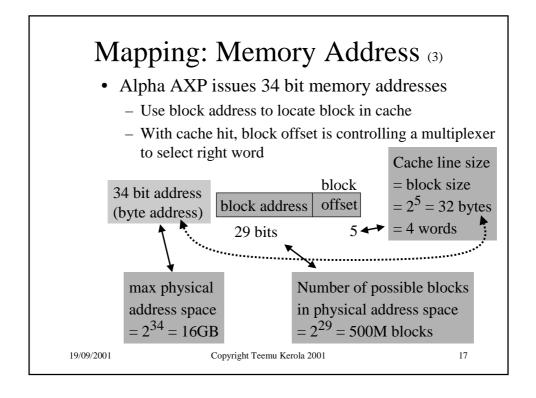

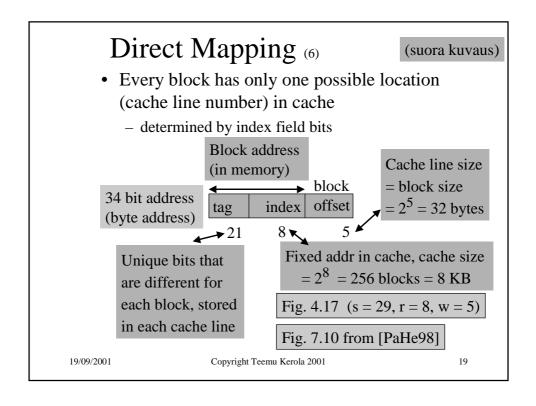

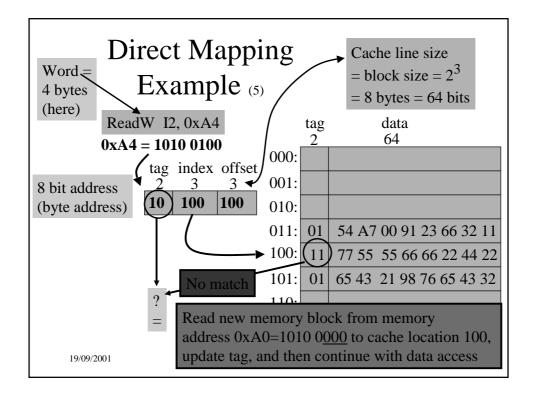

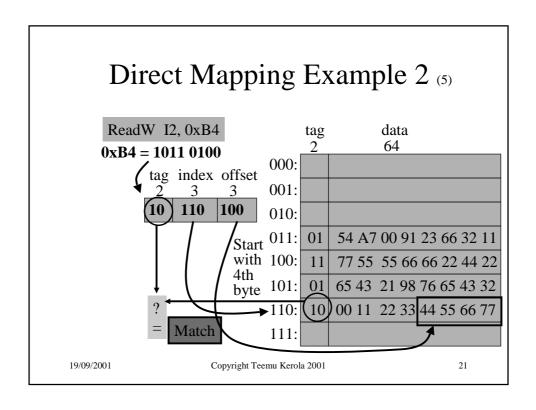

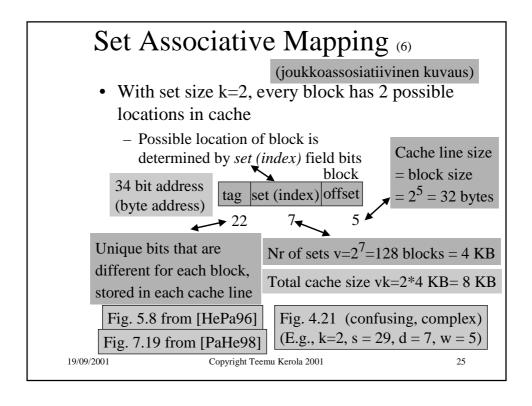

# $Mapping_{\ (2)}$

- Given a memory block address,

- is that block in cache?

- where is it there?

- Three solution methods

- direct mappings

- fully associative mapping

- set associative mapping

19/09/2001

Copyright Teemu Kerola 2001

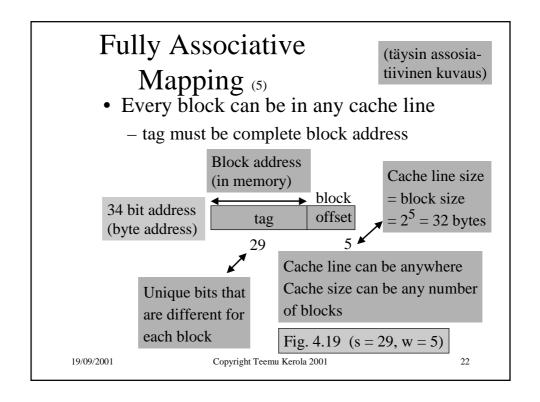

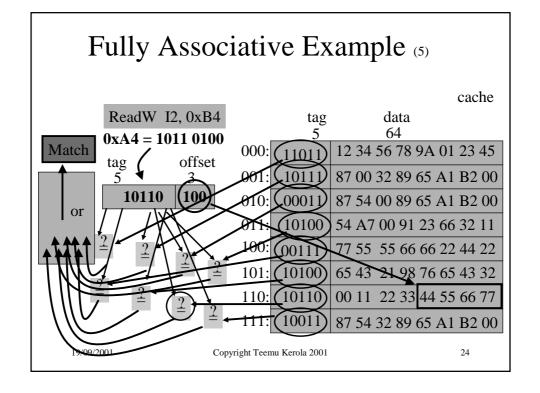

## Fully Associative Mapping

- Lots of circuits

- tag fields are long wasted space!

- each cache line tag must be compared simultaneously with the memory address tag

- · lots of wires

• lots of comparison circuits

Large surface area on chip

- Final comparison "or" has large gate delay

- did any of these 64 comparisons match?

$^{2}$  log(64) = 8 levels of binary gates

- how about 262144 comparisons? <sub>18 levels?</sub>

- $\Rightarrow$  Can use it only for small caches

19/09/2001

Copyright Teemu Kerola 2001

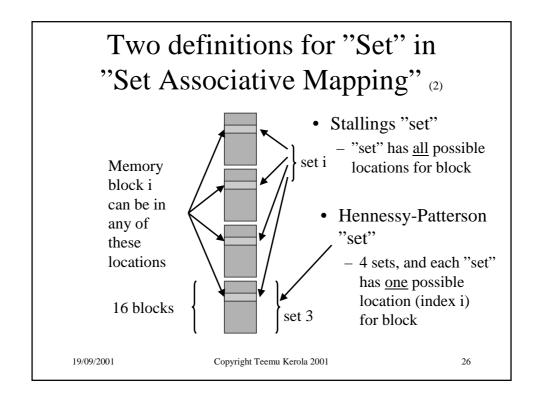

# Two definitions for "Set" in "Set Associative Mapping"

- Term "set" is the set of all possible locations where referenced memory block can be

- Field "set" of memory address determines this set

- [Stal99]

- Cache memory is split into multiple "sets", and the referenced memory block can be in only one location in each "set"

- Field "index" of memory address determines possible location of referenced block in each "set"

- [HePa96], [PaHe98]

19/09/2001

Copyright Teemu Kerola 2001

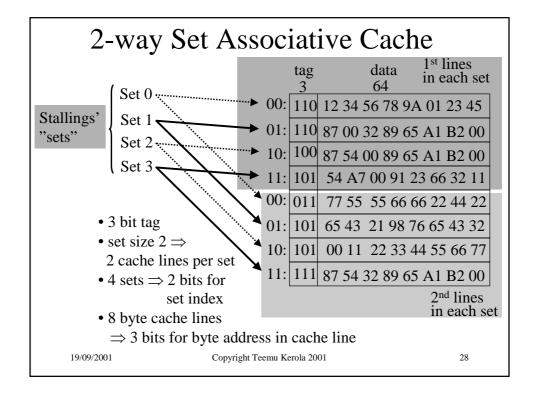

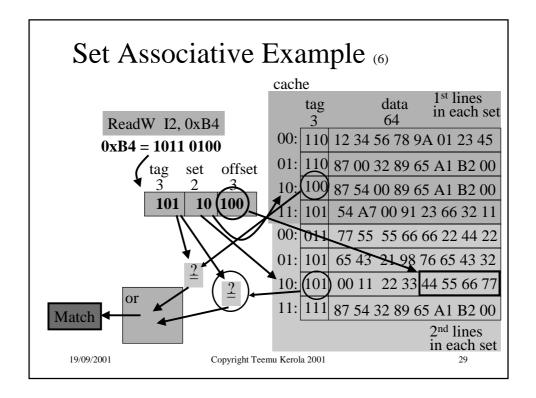

# Set Associative Mapping

- Set associative cache with set size 2

- = 2-way cache

- Degree of associativity v? Usually 2

- v large?

Fig. 7.16 from [PaHe98]

- More data items (v) in one set

- less "collisions"

- final comparison (matching tags?) gate delay?

- v maximum (nr of cache lines)

- $\Rightarrow$  fully associative mapping

- v minimum (1)  $\Rightarrow$  direct mapping

19/09/2001

Copyright Teemu Kerola 2001

## Replacement Algorithm

- Which cache block (line) to remove to make room for new block from memory?

- Direct mapping case trivial

- First-In-First-Out (FIFO)

- Least-Frequently-Used (LFU)

- Random

- Which one is best?

- Chip area?

- Fast? Easy to implement?

19/09/2001

Copyright Teemu Kerola 2001

31

## Write Policy

- How to handle writes to memory?

- Write through

(läpikirjoittava)

- each write goes always to memory

- each write is a cache miss!

(lopuksi kirjoittava takaisin kirjoittava?)

- Write back

- write cache block to memory only when it is replaced in cache

- memory may have stale (old) data

- cache coherence problem (välimuistin yhteneväisyysongelma)

19/09/2001

Copyright Teemu Kerola 2001

#### Line size

- How big cache line?

- Optimise for temporal or spatial locality?

- bigger is better for spatial locality

- <u>Data</u> references and <u>code</u> references behave in a different way

- Best size varies with <u>program</u> or <u>program phase</u>

- 2-8 words?

- word = 1 float??

19/09/2001

Copyright Teemu Kerola 2001

33

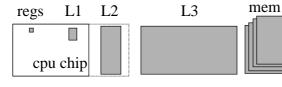

## Number of Caches (3)

- One cache too large for best results

- Unified vs. split cache

(yhdistetty, erilliset)

- same cache for data and code, or not?

- split cache: can optimise structure separately for data and code

- Multiple levels of caches

- L1 same chip as CPU

- L2 same package or chip as CPU

- L3 same board as CPU

Fig. 4.23

19/09/2001

Copyright Teemu Kerola 2001

#### -- End of Ch. 4.3: Cache Memory --

http://www.intel.com/procs/servers/feature/cache/unique.htm

"The Pentium® Pro processor's unique multi-cavity chip package brings L2 cache memory closer to the CPU, delivering higher performance for business-critical computing needs."

19/09/2001 Copyright Teemu Kerola 2001 35