### Instruction Sets Ch 9-10

Characteristics

Operands

Operations

Addressing

Instruction Formats

26/09/2001

Copyright Teemu Kerola 2001

### **Instruction Set**

(käskykanta)

- Collection of instructions that CPU understands

- Only interface to CPU from outside

- CPU executes a program ⇔ CPU executes given instructions "one at a time"

- fetch-execute cycle

Fig. 9.1

26/09/2001

Copyright Teemu Kerola 2001

# Machine Instruction Opcode - What should I do? Math? Move? Jump? Source operand references - Where is the data to work on? Reg? Memory? Result operand reference - Where should I put the result? Reg? Memory? Next instruction reference - Where is the next instruction? Default? Jump?

### Instruction Set Design (5)

• Operation types

(operaatiotyyppi)

- How many? What type? Simple? Complex?

• Data types

(tietotyyppi)

- Just a few? Many?

• Instruction format

(käskyn muoto)

- fixed length? Varying length? Nr of operands?

- Number of addressable registers

- too many  $\Rightarrow$  too long instructions?

- too few  $\Rightarrow$  too hard to optimise code?

- Addressing

(tiedon osoitus)

- What modes to use to address data and when?

26/09/2001

Copyright Teemu Kerola 2001

5

### Good Instruction Set (2)

- Good target to compiler

- Easy to compile?

- Possible to compile code that runs fast?

- Easy to compile code that runs fast?

- Allows fast execution of programs

- How many meaningless instructions per second? MIPS? GFLOPS?

- How fast does my program run?

- Solve linear system of 1000 variables?

- Set of data base queries?

- Connect a phone call in <u>reasonable</u> time?

26/09/2001

Copyright Teemu Kerola 2001

### Good Instruction Set (contd) (5)

- Beautiful & Aesthetic

- Orthogonal

(ortogonaalinen)

- Simple, no special registers, no special cases, any data type or addressing mode can be used with any instruction

- Complete

(täydellinen)

- Lots of operations, good for all applications

- Regular

(säännöllinen)

- Specific instruction field has always same meaning

- Streamlined

(virtaviivainen)

• Easy to define what resources are used

26/09/2001

Copyright Teemu Kerola 2001

-

### Good Instruction Set (contd) (2)

- Easy to implement

- 18 months vs. 36 months?

- Who will be 1<sup>st</sup> in market? Who will get development monies back and who will not?

- Scalability

(skaalautuva)

- Speed up clock speed 10X, does it work?

- Double address length, does design extend?

- E.g., 32 bits  $\Rightarrow$  64 bits  $\Rightarrow$  128 bits?

26/09/2001

Copyright Teemu Kerola 2001

### Number of Operands? (4)

- 3? ADD A,B,C  $Mem(A) \leftarrow mem(B) + mem(C)$

- Normal case now ADD R1, R2, R3  $r1 \leftarrow r2+r3$

- 2? ADD R1, R2  $r1 \leftarrow r1+r2$

- 1 operand and result the same

- 1? ADD A  $acc \leftarrow acc + mc$

- -1 operand and result in implicit  $\frac{\text{acc} \leftarrow \text{acc+mem(A)}}{\text{accumulator}}$

- 0?

- All operands and result in implicit stack

26/09/2001

Copyright Teemu Kerola 2001

## Instruction Set Architecture (ISA) Basic Classes

- Accumulator

- Stack

- General Purpose Register

- only one type of registers, good for all

- 2 or 3 operands

- Load/Store

- only load/store instructions access memory

LOAD R3, C LOAD R2,B ADD R1,R2,R3 STORE R1,A

– 3 operand ALU instructions

26/09/2001

Copyright Teemu Kerola 2001

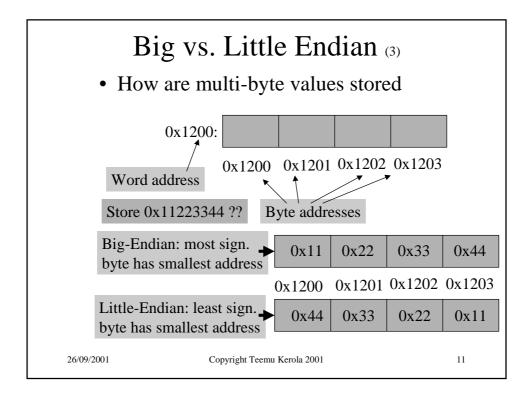

### Big vs. Little Endian

- Address of multi-byte data items is the same in both representations

- Only internal byte order varies

- Must decide one way or the other

- Math circuits must know which presentation used

- Little-Endian may be faster ....

- Must consider when moving data via network

- Power-PC: bi-endian both modes at use

- can change it per process basis

- kernel mode selected separately

26/09/2001

Copyright Teemu Kerola 2001

### Data (Operands, Result) Location

• Register

acc

r2, r8

- close, fast

register stack

f4, f15

- limited number of them

- need to load/store values from/to memory sometimes (often)

- Big problem! 50% of compiler time to decide

- register allocation problem

- Memory

memory stack (hw regs have mem addresses)

0x345670

- far away

- only possibility for large data sets

- vectors, arrays, sets, tables, objects, ...

26/09/2001

Copyright Teemu Kerola 2001

13

### Aligned Data (4)

2 byte (16-bit) half-word has byte address:

0010...1001<u>0</u>

4 byte (32-bit) word has byte address:

0010...101<u>00</u>

8 byte (64-bit) doubleword has byte address:

0010...11<u>000</u>

Aligned data

11 22 33 44

- faster memory access

- 32-bit data loaded as one memory load

- Non-aligned data

11 22

– saves mem, more bus traffic! 33

c! 33 44

• 32-bit non-aligned data requires 2 memory loads (each 4 bytes) and combining data into one 32-bit

data item

26/09/2001

Copyright Teemu Kerola 2001

### Data Types (8)

• Address 16b, 32b, 64b, 128b?

• Integer 16b, 32b, 64b?

• Floating point 32b, 64b, 80b?

• Decimal 18 digits (9 bytes) packed decimal?

• Character 1 byte = 8b IRA = ASCII, EBCDIC?

• String finite, arbitrary length?

• Logical data 1 bit (Boolean value, bit field)?

15

• Vector, array, record, ....

26/09/2001 Copyright Teemu Kerola 2001

Size of Operand

• 1 word, 32 bits int, float, addr

• 2 words, 64 bits double float, addr

• 4 words, 128 bits addr

• 1 byte (8 bits) char

• 2 bytes short int

• 1 bit logical values

26/09/2001 Copyright Teemu Kerola 2001 16

### Pentium II Data Types

- General data types

- 8-bit byte

- 16-bit word

- 32-bit doubleword

- 64-bit quadword

- Not aligned

- Little Endian

- Specific data types

- Numerical data types

Table 9.2

Figure 9.4

26/09/2001

Copyright Teemu Kerola 2001

17

### **Operation Types**

Table 9.3

- Data transfer

- CPU  $\leftrightarrow$  memory

- ALU operations

- INT, FLOAT, BOOLEAN, SHIFT, CONVERSION

- I/O

- read from device, start I/O operation

- Transfer of control

- jump, branch, call, return, IRET, NOP

- System control

- HALT, SYSENTER, SYSEXIT, ...

Table 9.4

- CPUID returns current HW configuration

- size of L1 & L2 caches, etc

26/09/2001

Copyright Teemu Kerola 2001

### Data References (2)

- Where is data?

- in memory

- in registers

- in instruction itself

- How to refer to data?

- various addressing modes

- multi-phase data access

- how is data location determined (addressing mode)

- compute data address (register? effective address?)

- · access data

26/09/2001 Copyright Teemu Kerola 2001 19

Copyright Teemu Kerola 2001

26/09/2001

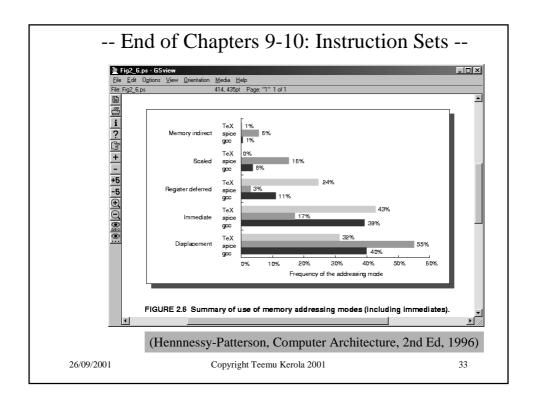

### Addressing Modes (Ch 10)

Fig. 10.1

Immediate

Data in instruction

Table. 10.1

Direct

Memory address of data in instruction

Indirect

Address of memory address of data in instruction (pointer)

Register

Data in register (best case?)

• Register Indirect

Register has memory address (pointer)

• Displacement

Addr = reg value + constant

• Stack

Data is stack pointed by some register

26/09/2001

Copyright Teemu Kerola 2001

21

### Displacement Address

• Effective address = (R1) + A

Contents of R1

Constant from instruction

- Constant is often small (8 bits, 16 bits?)

- Many uses

- PC relative

JUMP <u>-40(PC)</u>

Base register address

CALL <u>Summation(BX)</u>

Array index

ADDF F2, F2, Table(R5)

- Record field

MUL F4, F6, Salary(R8)

Stack references

STORE F2, <u>-4(FP)</u>

26/09/2001

Copyright Teemu Kerola 2001

### More Addressing Modes

size of operand

Autoincrement

$$EA = (R), R \leftarrow (R) + S$$

- E.g., R pointer to an array

- Autodecrement

$$R \leftarrow (R) - S, EA = (R)$$

- E.g., R pointer to an array

- Autoincrement deferred

$$EA = Mem(R), R \leftarrow (R) + S$$

- E.g., R pointer to an array of pointers

- Scaled

$$EA = A + (R_i) + (R_i) * S$$

- E.g., item  $(R_i, R_j)$  in 2-dimensional array A[i,j]

26/09/2001

Copyright Teemu Kerola 2001

23

### Pentium II Addressing Modes

- Immediate

- -1, 2, 4 bytes

- Register operand

- -1, 2, 4, 8 byte registers

- not all registers with every instruction

- Operands in Memory

Fig. 10.2

compute effective address and combine with segment register to get linear address (virtual address)

Table 10.2

26/09/2001

Copyright Teemu Kerola 2001

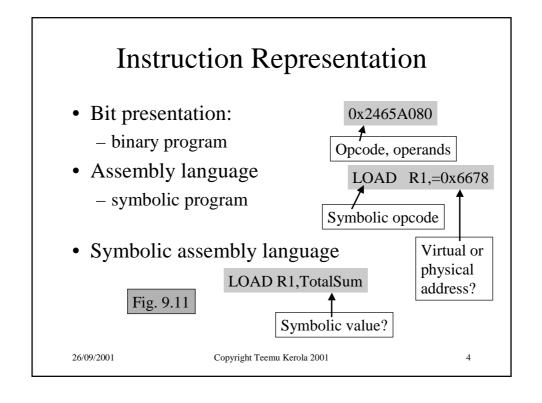

### Instruction Format (4)

- How to represent instructions in memory?

- How long instruction

- Descriptive or dense? Code size?

- Fast to load?

- In many parts?

- One operand description at a time?

- Fast to parse (I.e., split into logical components)?

- All instruction same size & same format?

- Very few formats?

26/09/2001

Copyright Teemu Kerola 2001

25

### Instruction Format (contd) (3)

- How many addressing modes?

- Fewer is better, but harder to compile to

- How many operands?

- 3 gives you more flexibility, but takes more space

- How many registers?

- 16 regs  $\rightarrow$  need 4 bits to name it

- $-256 \text{ regs} \rightarrow \text{need } 8 \text{ bits to name it}$

- need at least 16-32 for easy register allocation

- How many registers, that can be referenced in one instruction vs. referenced overall?

26/09/2001

Copyright Teemu Kerola 2001

### Instruction Format (contd) (3)

- How many register sets?

- A way to use more registers without forcing long instructions for naming them

- One register set for each subroutine call?

- One for indexing, one for data?

- Address range, number of bits in displacement

- more is better, but it takes space

- Address granularity

- byte is better, but word address is shorter

26/09/2001

Copyright Teemu Kerola 2001

27

### Pentium II Instruction Set (5)

- CISC Complex Instruction Set Computer

- At most one memory address

- "Everything" is optional

- "Nothing" is fixed

- Difficult to parse

- all latter fields and their interpretation depend on earlier fields

Fig. 10.8

26/09/2001

Copyright Teemu Kerola 2001

### Pentium II Instruction Prefix Bytes (4)

• Instruction prefix (optional)

Fig. 10.8 (a)

- LOCK exclusive use of shared memory

- REP repeat instruction for string characters

- Segment override (optional)

- override default segment register

- default is implicit, no need to store it every instruction

- Address size (optional)

- use the other (16 or 32 bit) address size

- Operand size (optional)

- use the other (16 or 32 bit) operand size

26/09/2001

Copyright Teemu Kerola 2001

29

### Pentium II Instruction Fields (3)

Opcode

Fig. 10.8 (b)

- specific bit for byte size data

- Mod r/m (optional)

- data in reg (8) or in mem?

- which addressing mode of 24?

- can also specify opcode further for some opcodes

- SIB (optional) Scale/Index/Base

- extra field needed for some addressing modes

- scale for scaled indexing

- index register

- base register

26/09/2001

Copyright Teemu Kerola 2001

# Pentium II Instruction Fields (contd) (2)

• Displacement (optional)

Fig. 10.8 (b)

- for certain addressing modes

- -1, 2, or 4 bytes

- Immediate (optional)

- for certain addressing modes

- -1, 2, or 4 bytes

26/09/2001

Copyright Teemu Kerola 2001

31

### PowerPC Instruction Format (7)

- RISC Reduced Instruction Set Computer

- Fixed length, just a few formats

Fig. 10.9

- Only load/store instructions access memory

- Only 2 addressing modes for data

- 32 general purpose registers can be used everywhere

- Fixed data size

- no string ops

- Simple branches

- CR-field determines which register to compare

- L-bit determines whether a subroutine call

- A-bit determines if branch is absolute or PC-relative

26/09/2001

Copyright Teemu Kerola 2001