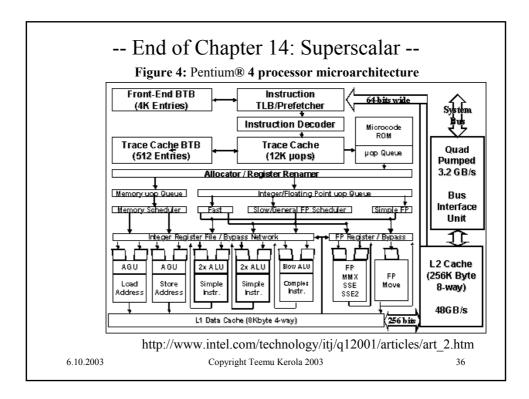

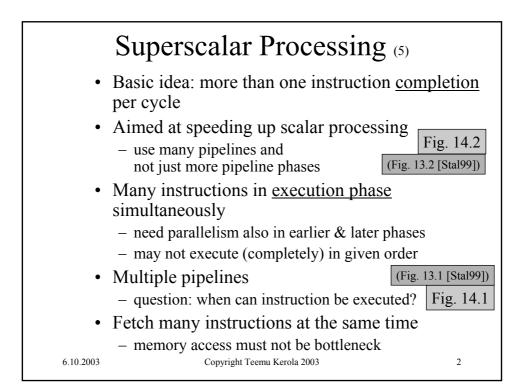

## Superscalar Processors Ch 14

Limitations, Hazards Instruction Issue Policy Register Renaming Branch Prediction PowerPC, Pentium 4

6.10.2003

Copyright Teemu Kerola 2003

1

## Overall Gain from Superscalar Implementation

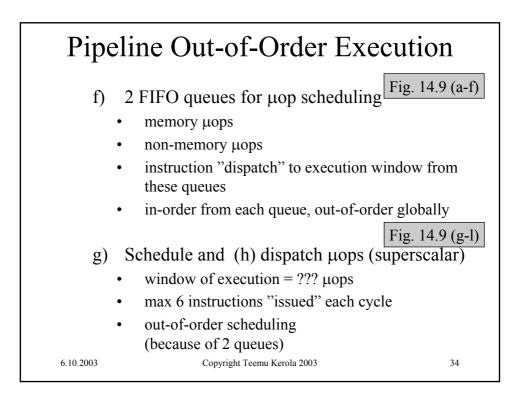

| Pipeline Out-of-Order Execution                          |                                                                                                                                       |                 |  |

|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|

| e) Allo                                                  | ocate resources                                                                                                                       | Fig. 14.9 (a-f) |  |

| - reorder buffer (ROB) entry (one of $\underline{126}$ ) |                                                                                                                                       |                 |  |

| • state: scheduled, dispatched, completed, ready         |                                                                                                                                       |                 |  |

| •                                                        | <ul> <li>original IA-32 instruction address</li> </ul>                                                                                |                 |  |

| •                                                        | μop and which operands for it are available                                                                                           |                 |  |

| •                                                        | alias register for result (one of 128 ROB registers<br>referencing one of 8 IA-32 register, or one of 48<br>load or 24 store buffers) |                 |  |

|                                                          | - true data dependencies solved with these                                                                                            |                 |  |

|                                                          | <ul> <li>false dependencies avoided by these</li> </ul>                                                                               |                 |  |

| •                                                        | 2 Register Alias Tables (RAT) keep track where<br>current version of each 8 IA-32 register (E.g.,<br>EAX) is                          |                 |  |

| 6.10.2003                                                | Copyright Teemu Kerola 2003                                                                                                           | 33              |  |