# Unrestricted vs restricted cut in a tableau method for Boolean circuits \*

Matti Järvisalo, Tommi Junttila \*\* and Ilkka Niemelä

Helsinki University of Technology, Laboratory for Theoretical Computer Science, P.O. Box 5400, F1-02015 TKK, Finland

E-mail: {matti.jarvisalo;tommi.junttila;ilkka.niemela}@tkk.fi

This paper studies the relative efficiency of variations of a tableau method for Boolean circuit satisfiability checking. The considered method is a nonclausal generalisation of the Davis–Putnam–Logemann–Loveland (DPLL) procedure to Boolean circuits. The variations are obtained by restricting the use of the cut (splitting) rule in several natural ways. It is shown that the more restricted variations cannot polynomially simulate the less restricted ones. For each pair of methods T, T', an infinite family  $\{C_n\}$  of circuits is devised for which T has polynomial size proofs while in T' the minimal proofs are of exponential size w.r.t. n, implying exponential separation of T and T' w.r.t. n. The results also apply to DPLL for formulas in conjunctive normal form obtained from Boolean circuits by using Tseitin's translation. Thus DPLL with the considered cut restrictions, such as allowing splitting only on the variables corresponding to the input gates, cannot polynomially simulate DPLL with unrestricted splitting.

Keywords: satisfiability, Boolean circuits, cut rule, proof complexity, DPLL

AMS subject classification: 03B70, 03F20, 68T15, 68T20

#### 1. Introduction

The propositional satisfiability problem (SAT) of determining whether a given propositional formula has a truth assignment under which it evaluates to true is an archetypical NP-complete problem, see, e.g., [26]. Because of its universal nature, a variety of important problems, e.g., in the areas of planning [19,20], model checking of finite state systems [4,5], testing [22], and hardware verification [3], can be reduced to SAT. Due to this, there is a high demand for more feasible ways of solving SAT instances, ranging from industrial applications to pure research. Various methods for solving SAT instances have been developed (see [14,32] for surveys) and applied successfully to many interesting domains.

Recognising the factors that affect the difficulty of satisfiability checking, i.e., the time needed to determine whether an instance is satisfiable or not, is crucial when developing more efficient methods for the task. The basis of most state-of-the-art SAT

<sup>\*</sup> The financial support from Academy of Finland (project #53695) is gratefully acknowledged.

<sup>\*\*</sup> This work was partially done while visiting ITC-IRST (Trento, Italy), and has been sponsored by the CALCULEMUS! IHP-RTN EC project, contract code HPRN-CT-2000-00102.

checkers today is the *Davis–Putnam–Logemann–Loveland procedure* (DPLL) [9,10]. The efficiency of a typical DPLL based SAT checking system depends on

- the applied search space pruning techniques, e.g., non-branching deduction rules, nonchronological backtracking (see, e.g., [24]), and conflict-driven learning (see, e.g., [31]), and on

- the *splitting rule*, i.e., on which Boolean variables to apply the *explicit cut* that induces branching, and what kind of *heuristics* is this decision based on.

For measuring the efficiency of SAT checking methods there are several alternatives. One can compare SAT checkers by *experimental evaluation*, i.e., investigate how long it takes for checkers to solve different types of instances. Another approach is *worst-case analysis* of SAT checking algorithms (see, e.g., [8]), i.e., giving analytic proofs of upper bounds on the running times of algorithms w.r.t. the instance size. A third approach, the one taken in this work, is to investigate how large the minimal-size proofs (refutations) are for different families of formulas. This measure is called *proof complexity*, see, e.g., [2]. Proof complexity is of our interest as it allows one to differentiate heuristic performance from the proof rules in a method and to consider how small proofs can be established assuming *optimal* heuristic behaviour.

Relative efficiency of proof systems can be measured using the notion of *polynomial simulation*. If a proof method T can polynomially simulate another method T', then T is considered to be at least as efficient as T'. Showing that T' cannot polynomially simulate T gives a way of establishing that T is substantially stronger than T'. This is because the lack of polynomial simulation means that moving from T to T' cannot be done with only a polynomial loss of efficiency, i.e., there are proofs in T which do not have any polynomial size counter-part in T'.

Currently most successful DPLL-based SAT checkers assume that the input formulas are in *conjunctive normal form* (CNF). The reason for this is that it is simpler to develop efficient data structures and algorithms for CNF than for arbitrary formulas. On the other hand, using CNF makes efficient modelling of an application cumbersome. Fortunately, propositional formulas can be transformed in polynomial time into CNF while preserving the satisfiability of the instance, see, e.g., [27]. Therefore one usually employs a more general formula representation in modelling and then transforms the formula into CNF. However, such a polynomial time translation introduces auxiliary variables which can have an exponential effect on the performance of a typical SAT checker in the worst-case.

In addition, by translating other representations to CNF one often hides information about the structure of the original problem. One way of representing propositional formulas in a more general, structure-preserving way is to use *Boolean circuits*, see, e.g., [26]. Basically, Boolean circuits are acyclic directed graphs in which the nodes – representing subformulas of the instance – are called *gates*, and the edges represent dependencies between the gates. Boolean circuits are interesting because they allow for a compact and natural representation that can be simplified by sharing common subexpressions, while preserving natural structures and concepts of the domain. Boolean circuits

can be translated into CNF using a standard translation often referred to as *Tseitin's translation* [30]. This translation introduces a new variable for each gate in the circuit, resulting in a linear size CNF.

In this work we are interested in solving Boolean circuit satisfiability problems using an approach that exploits the highly successful DPLL type techniques but works directly on circuits. One approach is to translate the circuit to CNF and use the clausal DPLL method as the basis but add extra information from the circuit to enhance the performance of the method. See, e.g., [13,23] for interesting work in this direction. Another approach is to develop a generalisation of the DPLL method that works directly on the circuit structure. This direction has been pursued, e.g., in [11,18,21,29]. Here we study the latter approach and use as the basis of the work a simplified version of a tableau method for Boolean circuit satisfiability checking that works directly with circuits [18] (see [17] for an implementation of the method). The method is a nonclausal generalisation of DPLL to Boolean circuits which does not include learning or nonchronological backtracking techniques (see [29] for recent work on incorporating these techniques to a generalised DPLL). The method is closely related to standard tableau techniques [6] but works directly on a circuit (rather than formula) representation. Moreover, it employs a direct cut rule combined with deterministic (nonbranching) deduction rules making it similar to the tableau system KE [7]. More information on the advantages of using a direct cut rule compared to typical cut free tableaux can be found in [6,7,25].

In this work we focus on the splitting/cut rule of the tableau method for Boolean circuits, the research problem being:

How do restrictions on the use of the cut rule affect proof complexity in Boolean circuit satisfiability checking based on tableaux?

For instance, one may think that it is a good idea to restrict the cuts to the *input gates* only as they determine the values of all other gates. Therefore, the search space for a circuit with K gates and N input gates,  $K \ge N$ , would be  $2^N$  instead of  $2^K$ . This approach is proposed, for example, in [12,13,28]. However, our results show that this kind of a restricted cut rule cannot polynomially simulate the unrestricted cut rule. In particular, we show that there is an infinite family  $\{C_n\}$  of circuits which have polynomial size proofs using the unrestricted cut rule but for which minimal proofs are of exponential size w.r.t. n if cuts are restricted to input gates only. In addition to the input gate restricted cuts, we study several other natural restrictions that are based on the structure of the circuit and the state of the search. Examples of such dynamic restrictions are "top-down" cuts that can be applied only on the children of the gates with a determined value in the current state of the search and "bottom-up" cuts that can be applied on input gates and on the parents of the already determined gates. Our results show that none of the considered restricted variations can polynomially simulate the unrestricted cut rule. Furthermore, we devise families of circuits for which the size of the proofs using different cut rules differs exponentially, i.e., for rules  $R_1$  and  $R_2$  we construct an infinite family  $\{C_n\}$  of circuits which have polynomial size proofs using  $R_2$  but for which minimal proofs are of exponential size in n using  $R_1$ , implying exponential separation of  $R_1$  and  $R_2$  w.r.t. n.

The main results in this paper directly apply to DPLL based SAT checkers without conflict-driven learning for CNF formulas obtained from Boolean circuits by using Tseitin's translation. This is because the rules of the introduced tableau method match those of DPLL under CNF clauses produced by Tseitin's translation.

The rest of this work is organised as follows. Basic concepts of Boolean circuits are introduced in section 2. The tableau method and its locality based variations are described in section 3. The concepts of proof complexity and polynomial simulation are explained in section 4. In addition, section 4 establishes some basic results concerning these concepts and the tableau method. The main results of this work with proofs are presented in section 5. The relevance of the results to the DPLL method is established in section 6. Finally, section 7 concludes and gives some future research directions based on this work.

#### 2. Boolean circuits

Informally, a *Boolean circuit* (see, e.g., [26]) is an acyclic directed graph in which the nodes are called *gates*. The gates can be divided into three categories: (i) a unique *output gate* with incoming edges but no outgoing edges, (ii) *intermediate gates* with both incoming and outgoing edges, and (iii) *input gates* with outgoing edges but no incoming edges. A Boolean function is associated to the output gate and each intermediate gate.

Formally, we present a Boolean circuit  $\mathcal{C}$  with the set of gates  $\mathcal{V}$  as a set of equations of the form  $v = f(v_1, \ldots, v_k)$ , where  $v, v_1, \ldots, v_k \in \mathcal{V}$  and f is a Boolean function. It is required that (i) each  $v \in \mathcal{V}$  has at most one equation, (ii) the equations are non-recursive, and (iii) exactly one gate (i.e., the output gate) does not appear on the right-hand side of any equation. We define the size of a Boolean circuit to be the number of gates and edges in the circuit. For a Boolean circuit  $\mathcal{C}$ , we denote the set of gates appearing in  $\mathcal{C}$  by  $V(\mathcal{C})$ .

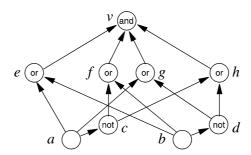

## **Example 1.** Graphically, the Boolean circuit

```

\{v = \text{and}(e, f, g, h), e = \text{or}(a, b), f = \text{or}(b, c), g = \text{or}(a, d), h = \text{or}(c, d), c = \text{not}(a), d = \text{not}(b) \}

```

is shown in figure 1. In this circuit, a and b are input gates, c, d, e, f, g and h intermediate gates, and v is the output gate.

A truth assignment for a Boolean circuit  $\mathcal{C}$  is a function  $\tau: V(\mathcal{C}) \to \{\text{true}, \text{false}\}$ . Assignment  $\tau$  is consistent if  $\tau(v) = f(\tau(v_1), \ldots, \tau(v_k))$  holds for each equation  $v = f(v_1, \ldots, v_k)$  in  $\mathcal{C}$ . A consistent truth assignment that assigns true to the output gate of a circuit is a satisfying truth assignment for the circuit. If there is a satisfying truth assignment for a circuit, the circuit is satisfiable. Otherwise the circuit is unsatisfiable.

Figure 1. A Boolean circuit.

Here, we are interested in CIRCUIT SAT, the *satisfaction problem* for Boolean circuits, in which we are given a Boolean circuit and asked whether the circuit is satisfiable. The CIRCUIT SAT problem is obviously NP-complete and closely related to SAT.

In the following we consider the class of Boolean circuits in which the following three types of Boolean functions are allowed.

- not(v) = true if and only if v is false,

- or $(v_1, \ldots, v_k)$  = true if and only if at least one  $v_i$ ,  $1 \le i \le k$ ,  $k \ge 2$ , is true, and

- and $(v_1, \ldots, v_k)$  = true if and only if all  $v_i, 1 \le i \le k, k \ge 2$ , are true.

Notice that it is straightforward to extend this class with additional Boolean functions such as xor and equivalence (see, e.g., [18]).

Consider a propositional formula in conjunctive normal form, i.e., a set  $\varphi = \{C_1, \dots, C_k\}$  of *clauses* of the form

$$C_i = (v_{i,1} \vee \cdots \vee v_{i,m_i} \vee \neg w_{i,1} \vee \cdots \vee \neg w_{i,n_i}).$$

The canonical Boolean circuit representation of  $\varphi$  is

$$\begin{split} C(\varphi) &= \big\{ v = \mathsf{and}(o_1, \dots, o_k) \big\} \\ &\quad \cup \big\{ o_i = \mathsf{or}(a_{v_{i,1}}, \dots, a_{v_{1,m_i}}, b_{w_{i,1}}, \dots, b_{w_{i,n_i}}) \mid 1 \leqslant i \leqslant k \big\} \\ &\quad \cup \big\{ b_{w_{i,i}} = \mathsf{not}(a_{w_{i,i}}) \mid 1 \leqslant i \leqslant k, 1 \leqslant j \leqslant n_i \big\}, \end{split}$$

where v is the output gate of  $C(\varphi)$ . It is straightforward to establish that the CNF formula  $\varphi$  is satisfiable if and only if the Boolean circuit  $C(\varphi)$  is satisfiable.

**Example 2.** In figure 1 the canonical Boolean circuit representation  $C(\text{UNSAT}_{a,b})$  is shown for

$$UNSAT_{a,b} \stackrel{\text{def}}{=} \{(a \lor b), (a \lor \neg b), (\neg a \lor b), (\neg a \lor \neg b)\}.$$

#### 3. A tableau method

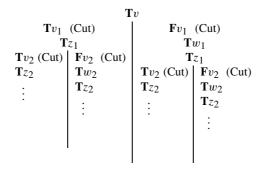

We study a tableau method for Boolean circuit satisfiability checking we call **BC**. The method consists of the rules shown in figure 2. It is a simplified version of the

$$\frac{v \in \mathcal{V}}{\mathbf{T}v \mid \mathbf{F}v}$$

(a) The explicit cut rule

$$v = \mathsf{not}(v_1) \qquad v = \mathsf{not}(v_1) \qquad v = \mathsf{not}(v_1) \qquad v = \mathsf{not}(v_1)$$

$$\frac{\mathbf{F}v_1}{\mathbf{T}v} \qquad \frac{\mathbf{T}v_1}{\mathbf{F}v} \qquad \frac{\mathbf{F}v}{\mathbf{T}v_1} \qquad \mathbf{F}v_1$$

(b) "Up" rules for not (c) "Down" rules for not

$$v = \mathsf{or}(v_1, \dots, v_k) \qquad v = \mathsf{or}(v_1, \dots, v_k) \qquad v = \mathsf{or}(v_1, \dots, v_k)$$

$$\frac{\mathbf{F}v_1, \dots, \mathbf{F}v_k}{\mathbf{F}v} \qquad \frac{\mathbf{T}v_i, i \in \{1, \dots, k\}}{\mathbf{T}v} \qquad \frac{\mathbf{F}v}{\mathbf{F}v_1, \dots, \mathbf{F}v_k}$$

(d) "Up" rules for or (e) "Down" rule for or

$$v = \mathsf{and}(v_1, \dots, v_k) \qquad v = \mathsf{and}(v_1, \dots, v_k) \qquad v = \mathsf{and}(v_1, \dots, v_k)$$

$$\frac{\mathbf{T}v_1, \dots, \mathbf{T}v_k}{\mathbf{T}v} \qquad \frac{\mathbf{F}v_i, i \in \{1, \dots, k\}}{\mathbf{F}v} \qquad \frac{\mathbf{T}v}{\mathbf{T}v_1, \dots, \mathbf{T}v_k}$$

(f) "Up" rules for and (g) "Down" rule for and

$$v = \mathsf{or}(v_1, \dots, v_k) \qquad v = \mathsf{and}(v_1, \dots, v_k)$$

$$\frac{\mathbf{F}v_1, \dots, \mathbf{F}v_{j-1}, \mathbf{F}v_{j+1}, \dots \mathbf{F}v_k}{\mathbf{T}v_1, \dots, \mathbf{T}v_{j-1}, \mathbf{T}v_{j+1}, \dots \mathbf{T}v_k}$$

$$\frac{\mathbf{T}v}{\mathbf{T}v_j} \qquad v = \mathsf{and}(v_1, \dots, v_k)$$

$$\frac{\mathbf{F}v_1, \dots, \mathbf{F}v_{j-1}, \mathbf{F}v_{j+1}, \dots \mathbf{F}v_k}{\mathbf{T}v_1, \dots, \mathbf{T}v_{j-1}, \mathbf{T}v_{j+1}, \dots \mathbf{T}v_k}$$

$$\frac{\mathbf{F}v}{\mathbf{F}v_j} \qquad \mathbf{F}v_j$$

(h) "Last undetermined child" rules for or and and

Figure 2. Tableau method BC for Boolean circuits.

tableau system introduced in [18]. The method is a nonclausal generalisation of DPLL to Boolean circuits: the explicit cut rule (a) in **BC** corresponds to the splitting rule in DPLL, and the rules (b)–(h) correspond to unit clause propagation, i.e., standard Boolean constraint propagation.

Given a Boolean circuit C, a **BC**-tableau for C is a binary tree such that the root node of the tree consists of the equations in C and additionally the entry Tv, where v is the output gate of C. The other nodes in the tree are entries of the form Tv or Fv, where  $v \in V(C)$ , generated by extending the tableau using the rules in figure 2 in the following standard way [6]. Given a tableau rule and a branch in the tableau such that the prerequisites of the rule hold in the branch, the tableau can be extended by adding new nodes to the end of the branch as specified by the rule. If the rule is (a), then entries Tv and Fv are added as the left and right child in the end of the branch. For the other rules, the consequents of the rule are added to the end of the branch (as a linear subtree in case of multiple consequents).

<sup>&</sup>lt;sup>1</sup> The method introduced in [18] provides additionally, e.g., rules for xor and equivalence gates as well as circuit simplification rules.

```

1. v = \operatorname{and}(e, f, g, h)

2. e = or(a, b)

3. f = or(b, c)

4. g = or(a, d)

5. h = or(c, d)

6. c = not(a)

7. d = not(b)

8. Tv

9. Te (1, 8)

10. T f (1, 8)

11. Tg (1, 8)

12. Th (1, 8)

13. Ta (Cut)

14. Fa (Cut)

15. Fc (6, 13)

20. Tb (2, 9, 14)

16. Tb (3, 10, 15) 21. Td (4, 11, 14)

17. Fd (7, 16)

22. Fd (7, 20)

18. Fh (5, 15, 17) | 23. × (21, 22)

19. \times (12, 18)

```

Figure 3. A **BC**-refutation for  $C(\text{UNSAT}_{a,b})$ .

A branch in the tableau is *contradictory* if it contains both  $\mathbf{F}v$  and  $\mathbf{T}v$  entries for a gate  $v \in V(\mathcal{C})$ . Otherwise, the branch is *open*. A branch is *complete* if it is contradictory, or if there is a  $\mathbf{F}v$  or a  $\mathbf{T}v$  entry for each  $v \in V(\mathcal{C})$  in the branch and the branch is closed under the rules (b)–(h). A tableau is *finished* if all the branches of the tableau are complete. A tableau is *closed* if all of its branches are contradictory. A closed  $\mathbf{B}\mathbf{C}$ -tableau for a circuit is called a  $\mathbf{B}\mathbf{C}$ -refutation for the circuit. For each  $v \in V(\mathcal{C})$ , we say that the entry  $\mathbf{T}v$  ( $\mathbf{F}v$ ) can be *deduced* in a branch if the entry  $\mathbf{T}v$  ( $\mathbf{F}v$ ) can be generated by applying rules (b)–(h) only.

**Example 3.** For the circuit shown in figure 1, a **BC**-refutation is shown in figure 3. For instance, in the refutation the entry  $\mathbf{F}c$  (15) is deduced from the entries  $c = \mathsf{not}(a)$  and  $\mathbf{T}a$ , while  $\mathbf{T}a$  (13) is generated by applying the cut rule.

We study variations of **BC** in which the application of the explicit cut rule is restricted to certain types of gates. The idea is to study the effects of restrictions which are based on the circuit structure. A natural starting point is a system where cuts are restricted to input gates only. A dynamic generalisation of this idea is to allow bottom—up cuts, i.e., to start from the input gates and permit the use of the cut rule in a tableau branch for a gate only when an entry for one of its children in the circuit has been deduced in the branch. A dual approach is to start from the entry of the output gate and allow top—down cuts. It is also possible to combine these approaches. The considered variations of **BC** are thus the following.

- **BC**<sub>i</sub>: Application of explicit cut is restricted to input gates (*input cuts*).

- $\mathbf{BC}_{bu}$ : Application of explicit cut in a branch is restricted to input cuts and gates v for which there is a  $\mathbf{T}v'$  or a  $\mathbf{F}v'$  entry in the branch for some child v' of v in the circuit (bottom-up cuts).

- $\mathbf{BC}_{td}$ : Application of explicit cut in a branch is restricted to the output gate and gates v for which there is a  $\mathbf{T}v'$  or a  $\mathbf{F}v'$  entry in the branch for some parent v' of v in the circuit ( $top-down\ cuts$ ).

- **BC**<sub>i+td</sub>: Application of explicit cut is restricted to input and top–down cuts.

- **BC**<sub>bu+td</sub>: Application of explicit cut is restricted to bottom-up and top-down cuts.

By soundness we mean that the existence of a closed tableau for a given circuit implies that the circuit is unsatisfiable, and by completeness that there is a closed tableau for any unsatisfiable circuit.

The following soundness theorem follows straightforwardly from the observation that the deduction rules (b)–(h) preserve satisfiability, i.e., if the premises of a rule are consistent for a truth assignment, then so is the conclusion.

**Theorem 1.**  $BC_i$ ,  $BC_{td}$ ,  $BC_{i+td}$ ,  $BC_{bu}$ ,  $BC_{bu+td}$ , and BC are sound proof systems for Boolean circuits.

The following completeness theorem is obvious by the cut rule. Input cuts with the deduction rules (b)–(h) are sufficient in order to obtain a complete branch. Moreover, input cuts can be simulated with top–down cuts in a straightforward manner.

**Theorem 2.**  $BC_i$ ,  $BC_{td}$ ,  $BC_{i+td}$ ,  $BC_{bu}$ ,  $BC_{bu+td}$ , and BC are complete proof systems for Boolean circuits.

# 4. Propositional proof complexity and simulation

Generally, a *propositional proof* is a certificate for the unsatisfiability of a propositional expression (e.g., of a propositional formula or Boolean circuit). A *propositional proof system* (see, e.g., [2]) for a class of propositional expressions E is then a polynomial-time computable predicate E such that for all expressions E it holds that E is unsatisfiable if and only if there is a proof E for E such that E is a E exist, it is a E-proof for E.

For instance, resolution is a propositional proof system that produces proofs for the unsatisfiability (i.e., refutations) of propositional formulas in conjunctive normal form. Similarly, **BC** is a propositional proof system for the unsatisfiability of Boolean circuits.

Let T be a proof system. The *proof complexity* (or *complexity* in short) of a propositional expression  $\alpha$  in T is the size of a minimal T-proof for  $\alpha$ . The *size of a resolution refutation* is defined in the standard way as the number of resolution steps in the refutation sequence. We define the *size of a* **BC**-refutation as the number of nodes in the closed tableau. For example, the size of the **BC**-refutation shown in figure 3 is 14.

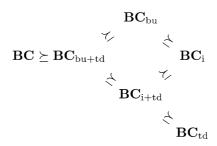

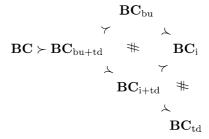

Figure 4. An obvious ordering of BC and its variations based on the polynomial simulation relation.

We use the notion of *polynomial simulation* to study the relative efficiency of proof systems. For any two proof systems T and T', we say that T *polynomially simulates* T', denoted by  $T \succeq T'$ , if there is a polynomial q such that, for any  $\alpha$ , if there is a T'-proof for  $\alpha$  of size n, then there is a T-proof for  $\alpha$  of size at most q(n). Hence,  $T \succeq T'$  indicates that the proof system T is at least as strong as T' (up to a polynomial loss of efficiency). The relation  $\succeq$  is transitive. If  $T \succeq T'$  holds but  $T' \succeq T$  does not, we write  $T \succ T'$ . If neither  $T \succeq T'$  nor  $T' \succeq T$  holds, we write  $T \not= T'$ .

We denote by  $\succeq_{\chi}$  the restricted form of polynomial simulation, in which  $T \succeq_{\chi} T'$  holds if there is a polynomial q such that, for any  $\alpha \in \chi$ , if there is a T'-proof for  $\alpha$  of size n, then there is a T-proof for  $\alpha$  of size at most q(n). If both  $T \succeq_{\chi} T'$  and  $T' \succeq_{\chi} T$  hold, we write  $T \equiv_{\chi} T'$ .

An obvious ordering of **BC** and its restricted variations based on the polynomial simulation relation, resulting from the restricted nature of the variations, is shown in figure 4.

It turns out that all the considered variations of the **BC** method are equivalent under the polynomial simulation relation when the set of propositional expressions considered is restricted to the set of canonical Boolean circuit representations of sets of clauses. For the following, let  $\Phi$  be the family of all sets of clauses, and  $C(\Phi) = \{C(\varphi) \mid \varphi \in \Phi\}$ .

## **Theorem 3.** BC $\equiv_{C(\Phi)}$ BC<sub>i</sub>.

To see this, notice that for any set of clauses  $\varphi$ , using the "down" rule for and we can deduce  $\mathbf{T}g$  for all or gates g in  $C(\varphi)$ . Thus we can assume that there is a minimal-size refutation for  $C(\varphi)$  in which the and rule is applied to deduce the entries concerning the or gates that are needed to achieve the closed tableau. Then it is straightforward to see that we can limit the application of the cut rule to input gates. This shows  $\mathbf{BC}_i \succeq_{C(\Phi)} \mathbf{BC}$ , while  $\mathbf{BC} \succeq_{C(\Phi)} \mathbf{BC}_i$  holds trivially.

By further noticing that for any circuit in the family  $C(\Phi)$  input cuts can be polynomially simulated with top–down cuts in a straightforward manner, we have the following corollary.

**Corollary 1.** BC

$$\equiv_{C(\Phi)} T$$

for all  $T \in \{BC_i, BC_{td}, BC_{i+td}, BC_{bu}\}.$

The following theorem states that, for the canonical Boolean circuit representation of a set of clauses, **BC**-proofs can be simulated by *tree-like* resolution. This is fairly straightforward to establish from a well-known construction for reading a tree-like resolution refutation from a DPLL refutation, see, e.g., [1].

**Theorem 4.** There is a polynomial p such that for any set of clauses  $\varphi$ , if there is a **BC**-refutation for  $C(\varphi)$  of size n, then there is a tree-like resolution refutation for  $\varphi$  of size p(n).

Again, by the restricted nature of the variants of the **BC** method, we have the following corollary.

**Corollary 2.** For each  $T \in \{\mathbf{BC_i}, \mathbf{BC_{td}}, \mathbf{BC_{bu}}, \mathbf{BC_{bu}}, \mathbf{BC_{bu+td}}\}\$  it holds that there is a polynomial p such that for any set of clauses  $\varphi$ , if there is a T-refutation for  $C(\varphi)$  of size p, then there is a tree-like resolution refutation for  $\varphi$  of size p(n).

We note that tree-like resolution (and thus DPLL) and **BC** are equally efficient proof systems in the sense that (i) given a set of clauses  $\varphi$ , **BC** on  $C(\varphi)$  can polynomially simulate tree-like resolution on  $\varphi$  and, moreover, (ii) given a circuit  $\mathcal{C}$  and the set of clauses  $\varphi_{\mathcal{C}}$  obtained from  $\mathcal{C}$  using Tseitin's translation, DPLL and thus tree-like resolution on  $\varphi_{\mathcal{C}}$  can polynomially simulate **BC** on  $\mathcal{C}$ . The latter fact is discussed in more detail in section 6 in which it is shown that the rules of **BC** match those of DPLL.

## 5. Relative efficiency of restricted cuts

The main results of this paper are summarised in figure 5 showing that there is no two-way polynomial simulation between the variations of the **BC** method. The results shed new light on the strength of proof systems of this kind, where the strength of the system is measured as the size of the minimal proofs producible for a given proposition. The results show that it is possible to increase the strength of a system significantly by extending the use of the cut rule in a controlled local manner w.r.t. the circuit struc-

Figure 5. Summary of the ordering of BC and its restricted variations based on the polynomial simulation relation. The case  $BC_{bu} \# BC_{td}$  is omitted from the picture for clarity.

ture. For example, moving from input cuts to bottom—up cuts can make a substantial difference in the sense that input cuts cannot polynomially simulate bottom—up cuts. If top—down cuts are additionally allowed, a similar substantial increase in the strength of the system is obtained. However, general cuts are still substantially stronger than any of the restricted variations considered. It should be noticed that the results obviously hold for circuits with additional Boolean functions if the set of rules involving and, or, and not gates remains unchanged. Furthermore, the results imply that the restrictions on the splitting rule in DPLL have the same effect on the proof complexity of CNF formulas obtained from Boolean circuits by using Tseitin's translation as will be discussed in section 6.

The rest of this section is devoted to proofs of these results. The proofs rely on certain circuit families which are constructed from building blocks such as a Boolean circuit representation of the pigeon-hole principle. First we define the building blocks we call *gadgets* and then give the proofs of the main theorems 6–14. Combining these theorems, the resulting ordering of **BC** and its restricted variations based on the polynomial simulation relation, shown in figure 5, is obtained by the transitivity of  $\succeq$ .

#### 5.1. Gadget constructions

We begin by defining the  $PHP_n^{n+1}$ ,  $TD_n$ ,  $XOR_n$ , and UNSAT gadgets. They are used in constructing families of circuits which are used in proving the main theorems of this paper. Some lemmas involving properties of the gadgets are given.

# 5.1.1. Pigeon-hole principle and the $PHP_n^{n+1}$ gadget

An example of a propositional formula with high proof complexity in many proof systems is the *pigeon-hole principle*  $PHP_n^m$ , see, e.g., [16]. The pigeon-hole principle states that there is no injective mapping from a finite m-element set into a finite n-element set if m > n (that is, m pigeons cannot sit in less than m holes so that every pigeon has its own hole). In the following we consider the case m = n + 1. As a set of clauses, we have

$$PHP_n^{n+1} \stackrel{\text{def}}{=} \bigcup_{1 \leqslant i \leqslant n+1} \{P_i\} \cup \bigcup_{1 \leqslant i < i' \leqslant n+1, 1 \leqslant j \leqslant n} \{H_{i,i'}^j\},$$

where the clauses  $P_i$  and  $H_{i,i'}^j$  are defined as  $P_i \stackrel{\text{def}}{=} \bigvee_{j=1}^n x_{i,j}$  and  $H_{i,i'}^j \stackrel{\text{def}}{=} (\neg x_{i,j} \lor \neg x_{i',j})$ , and each  $x_{i,j}$  is a Boolean variable with the interpretation " $x_{i,j} = \text{true}$  if and only if the ith pigeon sits in the jth hole". The  $P_i$  clauses state that each pigeon has to sit in some hole, while clauses  $H_{i,i'}^j$  state that no two pigeons can sit in the same hole. The union of all the clauses  $P_i$  and  $H_{i,i'}^j$  is obviously (by the pigeon—hole principle) unsatisfiable.

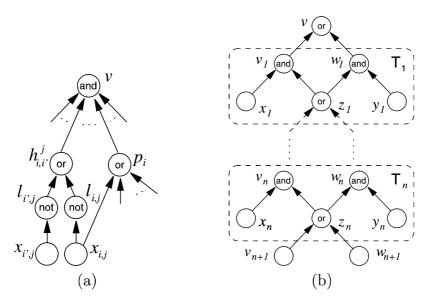

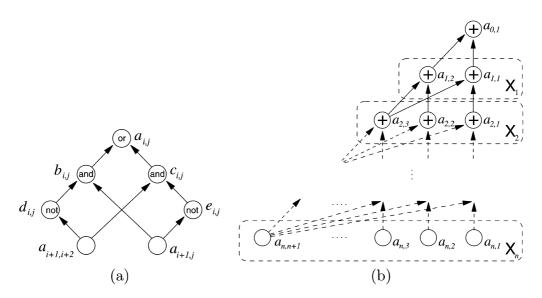

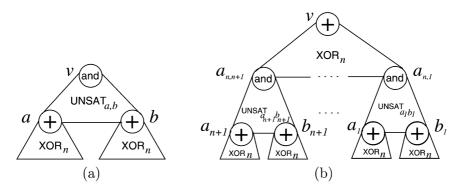

The canonical Boolean circuit representation of  $PHP_n^{n+1}$  is shown in part in figure 6(a). We call  $C(PHP_n^{n+1})$  the  $PHP_n^{n+1}$  gadget. Notice that as  $PHP_n^{n+1}$  is un-

Figure 6. (a) A part of the  $PHP_n^{n+1}$  gadget in detail, (b) the structure of the TD gadget.

satisfiable, so is  $C(PHP_n^{n+1})$ . Formally the  $PHP_n^{n+1}$  gadget is the set of equations

$$\begin{split} C\big(\mathsf{PHP}^{n+1}_n\big) &= \big\{v = \mathsf{and}(p_1, \dots, p_{n+1}, h^1_{1,2}, \dots, h^n_{n+1,n})\big\} \\ &\quad \cup \big\{p_i = \mathsf{or}(x_{i,1}, \dots, x_{i,n}) \mid 1 \leqslant i \leqslant n+1\big\} \\ &\quad \cup \big\{h^j_{i,i'} = \mathsf{or}(l_{i,j}, l_{i',j}) \mid 1 \leqslant i \lessdot i' \leqslant n+1, 1 \leqslant j \leqslant n\big\} \\ &\quad \cup \big\{l_{i,j} = \mathsf{not}(x_{i,j}) \mid 1 \leqslant i \leqslant n+1, 1 \leqslant j \leqslant n\big\}, \end{split}$$

where  $h_{1,2}^1, \ldots, h_{n+1,n}^n$  stands for all  $h_{i,i'}^j$ , where  $1 \le i < i' \le n+1$  and  $1 \le j \le n$ . By the results in [15] we have the following theorem.

**Theorem 5.** The size of the minimal resolution refutations for  $PHP_n^{n+1}$  is exponential w.r.t. n.

Combining theorem 4, corollary 2, and theorem 5, we have the following corollary.

**Corollary 3.** For each  $T \in \{\mathbf{BC_i}, \mathbf{BC_{td}}, \mathbf{BC_{bu}}, \mathbf{BC_{bu}}, \mathbf{BC_{bu+td}}, \mathbf{BC}\}$ , the size of the minimal T-refutations for  $C(\mathsf{PHP}_n^{n+1})$  is exponential w.r.t. n.

We use the pigeon–hole principle formulas because they are well known and the family  $\{PHP_n^{n+1}\}$  has some nice features: (i) the size of each  $PHP_n^{n+1}$  CNF instance is polynomial w.r.t. n, and (ii) the size of the minimal resolution refutation for  $PHP_n^{n+1}$  is exponential w.r.t. n. Notice that other hard CNF formula families with similar properties could have been used instead.

# 5.1.2. The TD gadget

The structure of the  $TD_n$  gadget is shown in figure 6(b). Formally the  $TD_n$  gadget is the set of equations

$$\begin{aligned} \text{TD}_n &= \left\{ v = \text{or}(v_1, w_1) \right\} \\ &\quad \cup \left\{ v_i = \text{and}(x_i, z_i) \mid 1 \leqslant i \leqslant n \right\} \\ &\quad \cup \left\{ w_i = \text{and}(y_i, z_i) \mid 1 \leqslant i \leqslant n \right\} \\ &\quad \cup \left\{ z_i = \text{or}(v_{i+1}, w_{i+1}) \mid 1 \leqslant i \leqslant n \right\}. \end{aligned}$$

The following lemma on the TD<sub>n</sub> gadget will be useful in the proofs of our main results. This lemma derives from the fact that in order to have an entry for gate  $z_n$  in every branch of a **BC**<sub>td</sub> tableau, one has to apply the cut rule on  $v_i$  or  $w_i$  for each  $1 \le i \le n$ , which leads to having an exponential number of entries in the tableau w.r.t. n.

**Lemma 1.** Every  $\mathbf{BC}_{td}$ -tableau for  $\mathrm{TD}_n$  in which each branch has an entry for the gate  $z_n$  is of exponential size w.r.t. n.

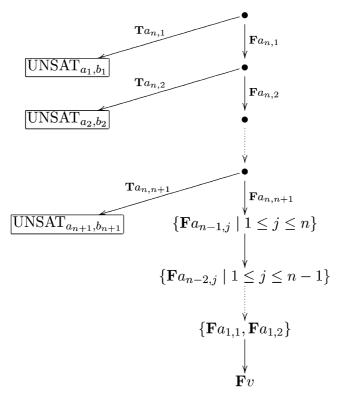

*Proof.* The entry  $\mathbf{T}v$  implies  $\mathbf{T}v_1$  or  $\mathbf{T}w_1$ , but we cannot deduce one or the other. Thus we must apply the cut rule on either  $v_1$  or  $w_1$  in  $\mathbf{BC}_{\mathrm{td}}$ . Assume that we cut on  $v_1$  (cutting on  $w_1$  is symmetric). Now consider the branch in which we have  $\mathbf{F}v_1$ . Due to  $v = \mathrm{or}(v_1, w_1)$  we must have  $\mathbf{T}w_1$ . Then from  $w_1 = \mathrm{and}(y_1, z_1)$  we deduce  $\mathbf{T}y_1$  and  $\mathbf{T}z_1$  in the branch. In the branch where we have  $\mathbf{T}v_1$  using the "down" rule for and we deduce  $\mathbf{T}x_1$  and  $\mathbf{T}z_1$ . Nothing else can be deduced. Inductively on i, in order to have an entry for the gate  $z_i$  in every branch of the tableau, the tableau must contain at least  $z^i$  branches, all of which remain open. This is because we must for each i apply the cut rule on either  $v_i$  or  $w_i$ . This is demonstrated in figure 7. Thus every tableau in which there is an entry for the gate  $z_n$  in every branch of the tableau is of size at least in the order of  $z^n$ , that is,  $z^{|V(\mathrm{TD}_n)|/5}$ .

Figure 7. Why **BC**<sub>td</sub>-refutations for the circuit in figure 6(b) are large.

Figure 8. (a) The Boolean function xor as a Boolean circuit, (b) the structure of the  $XOR_n$  gadget.

#### 5.1.3. The XOR gadget

The Boolean xor function  $xor(x, y) = (x \land \neg y) \lor (\neg x \land y)$  evaluates to true if and only if exactly one of x, y is true. Based on the xor function we can construct a Boolean circuit, as shown in figure 8(a), for which it holds that the output gate  $a_{i,j}$  evaluates to true if and only if  $xor(a_{i+1,i+2}, a_{i+1,j})$  evaluates to true. When we use this circuit construct as a part of a circuit, we represent it graphically as an "xor gate"  $\oplus$ .

Using the "xor gate" we construct a family of XOR<sub>n</sub> gadgets as shown in figure 8(b), having n layers  $X_i$ ,  $1 \le i \le n$ , of xor gates. Formally, the XOR<sub>n</sub> gadget is the set of equations

$$\begin{aligned} \text{XOR}_n &= \left\{ a_{i,j} = \text{or}(b_{i,j}, c_{i,j}) \mid 0 \leqslant i < n, 1 \leqslant j \leqslant i + 1 \right\} \\ & \cup \left\{ b_{i,j} = \text{and}(d_{i,j}, a_{i+1,j}) \mid 0 \leqslant i < n, 1 \leqslant j \leqslant i + 1 \right\} \\ & \cup \left\{ c_{i,j} = \text{and}(e_{i,j}, a_{i+1,i+2}) \mid 0 \leqslant i < n \right\} \\ & \cup \left\{ d_{i,j} = \text{not}(a_{i+1,i+2}) \mid 0 \leqslant i < n \right\} \\ & \cup \left\{ e_{i,j} = \text{not}(a_{i+1,j}) \mid 0 \leqslant i < n, 1 \leqslant j \leqslant i + 1 \right\}. \end{aligned}$$

The following two lemmas on the  $XOR_n$  gadget will be useful in the proofs of our main results. The lemmas derive from the property of the xor gate that, disregarding gates  $b_{i,j}$ ,  $c_{i,j}$ ,  $d_{i,j}$ ,  $e_{i,j}$ , one cannot deduce an entry for one of  $a_{i,j}$ ,  $a_{i+1,j}$ ,  $a_{i+1,i+2}$  without having an entry for both of the other two gates in the branch. This leads to the observation that in order to reach the output gate with bottom—up cuts or an input gate with top—down cuts one must apply the cut rule a number of times linear in n, and thus to having an exponential number of entries in the tableau w.r.t. n.

**Lemma 2.** Every  $\mathbf{BC}_{bu}$ -tableau for  $XOR_n$  in which each branch has an entry for the gate  $a_{1,1}$  or  $a_{1,2}$  is of exponential size w.r.t. n.

*Proof.* We show by induction on n that every  $\mathbf{BC}_{bu}$ -tableau for  $XOR_n$  in which each branch has an entry for the gate  $a_{1,1}$  or  $a_{1,2}$  is of size at least  $2^n$ .

For n = 1, we must use the cut rule first on  $a_{1,2}$  or  $a_{1,1}$ . Thus the branch has 1 application of the cut rule and the whole tableau is at least of size  $2^1$ .

Now assume that the lemma holds for n. Suppose that for  $XOR_{n+1}$  there is a **BC**<sub>bu</sub>tableau of size less than  $2^{n+1}$  in which there is in each branch an entry for  $a_{1,1}$  or  $a_{1,2}$ . In such a tableau, we must use the cut rule first on one of the gates  $a_{n+1,j}$ ,  $1 \le j \le n+2$ . Due to the xor-nature of the a gates and the use of bottom-up cuts, no gate of form  $a_{k,l}, k \leq n$ , can have a deduced entry before we have an entry for the gate  $a_{n+1,n+2}$ (produced either (i) by a cut on  $a_{n+1,n+2}$ , or (ii) by a cut on an undetermined gate  $b_{n,j}$ or  $c_{n,j}$  such that a cut was already made on  $a_{n+1,j}$ , forcing an entry for  $a_{n+1,n+2}$ , too). Therefore, we can assume that the first cut was actually made on  $a_{n+1,n+2}$ . Because of the assumption that the size of the tableau is less than  $2^{n+1}$ , one of the subtableaux below this cut has size less than  $2^n$ . In such a subtableau, if the gate  $a_{n+1,n+2}$  has an entry  $\mathbf{F}a_{n+1,n+2}$ , the gate  $a_{n,m}$  has an entry  $\mathbf{F}a_{n,m}$  ( $\mathbf{T}a_{n,m}$ ) if and only if the gate  $a_{n+1,m}$  has an entry  $\mathbf{F}a_{n+1,m}$  ( $\mathbf{T}a_{n+1,m}$ ). Similarly, if the gate  $a_{n+1,n+2}$  has an entry  $\mathbf{T}a_{n+1,n+2}$ , the gate  $a_{n,m}$  has an entry  $\mathbf{F}a_{n,m}$  ( $\mathbf{T}a_{n,m}$ ) if and only if the gate  $a_{n+1,m}$  has an entry  $\mathbf{T}a_{n+1,m}$ ( $\mathbf{F}a_{n+1,m}$ ). Therefore, if we have made a cut on a gate  $a_{n+1,m}$  in the subtableau, we could have equivalently made a cut on  $a_{n,m}$ . By replacing each such cut on  $a_{n+1,m}$  with a cut on  $a_{n,m}$  and removing other entries on gates not appearing in XOR<sub>n</sub>, we transform the subtableau for  $XOR_{n+1}$  to a **BC**<sub>bu</sub>-tableau for  $XOR_n$  having size less than  $2^n$ . But this contradicts the induction hypothesis and thus both subtableaux must have size at least  $2^n$ and the whole **BC**<sub>bu</sub>-tableau for XOR<sub>n+1</sub> is of size at least in the order of  $2^{n+1}$ .

**Lemma 3.** Every  $\mathbf{BC}_{td}$ -tableau for  $XOR_n$  in which each branch has an entry for some gate  $a_{n,i}$ ,  $1 \le i \le n+1$ , is of exponential size w.r.t. n.

*Proof.* As shown in figures 9 and 10, in order to deduce an entry for  $a_{i+1,j}$  or  $a_{i+1,i+2}$  from an entry for  $a_{i,j}$ , one has to apply the cut on one of the gates in the xor gate. This causes branching, while no branches can be closed.

By branching on  $b_{0,1}$  (or symmetrically on  $c_{0,1}$ ), we can thus deduce entries for both  $a_{1,1}$  and  $a_{1,2}$  in both branches. Thus in each branch we may continue as in either of Figures 9 or 10. Notice that after branching we have an entry for  $a_{i+1,i+2}$  in every branch. In addition to entries for all  $a_{i,j}$ , where  $1 \le j \le i+1$ , this is enough to deduce entries for all  $a_{i+1,j}$ . Still, for every i, we must apply the cut on some gate on level i to deduce entries for the gates  $a_{i+1,j}$ ,  $1 \le j \le i+2$ , doubling the number of open branches for each i. Thus every tableau in which there is in every branch an entry for some gate  $a_{n,i}$ ,  $1 \le i \le n+1$ , is of size at least in the order of  $2^n$ , that is,  $2^{\sqrt{|V(XOR_n)|}}$ .

Figure 9. A top-down subtableau for the xor circuit with an  $\mathbf{F}a_{i,j}$  entry.

Figure 10. A top-down subtableau for the xor circuit with a  $Ta_{i,j}$  entry.

#### 5.2. **BC**<sub>bu</sub> *vs* **BC**<sub>i</sub>

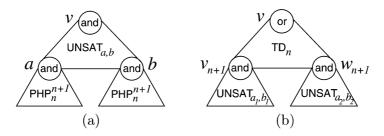

We now show that  $\mathbf{BC}_i$  cannot polynomially simulate  $\mathbf{BC}_{bu}$ . The proof utilises the UNSAT (i.e., the circuit shown in figure 1) and  $PHP_n^{n+1}$  gadgets.

**Lemma 4.** There is an infinite family  $\{C_n\}$  of circuits such that (i) the size of  $C_n$  is  $\mathcal{O}(n^3)$ , and (ii) there is a  $\mathbf{BC}_{bu}$ -refutation for  $C_n$  of constant size while any minimal  $\mathbf{BC}_{i}$ -refutation for  $C_n$  is of size exponential in n.

*Proof.* Consider the family of circuits of the type shown in figure 11(a). Any circuit in the family is obviously unsatisfiable. For an arbitrary n, for  $\mathbf{BC}_{bu}$  we can construct a constant size refutation as follows. First, deduce  $\mathbf{T}e$ ,  $\mathbf{T}f$ ,  $\mathbf{T}g$ ,  $\mathbf{T}h$  from  $\mathbf{T}v$ . Then apply (say, in the  $PHP_n^{n+1}$  gadget on the left) the cut rule first on one of the input gates  $x_{i,j}$ , and deduce an entry for  $l_{i,j}$ . After this, apply the cut rule on  $h_{i,i'}^j$  in both of the induced branches. Now we have induced four branches in total, having in each branch a constant number of entries, and can apply the cut rule on a in each branch. After having an entry on a, each branch can be closed in a constant number of steps similarly to the refutation shown in figure 3. Thus the generated closed tableau is of constant size.

Notice that to generate a refutation we need to reach the UNSAT gadget, i.e., it is impossible to generate a contradiction in all the branches of a tableau without having an entry for some of the gates in the UNSAT gadget in the tableau.

Now consider  $BC_i$ . From Tv we can deduce Te, Tf, Tg, and Th, but nothing else. As  $PHP_n^{n+1}$  is unsatisfiable, it is impossible to deduce Ta or Tb with "up" rules. Thus

Figure 11. (a) Circuit for theorems 6 and 7. (b) Circuit for theorem 8.

we can only have  $\mathbf{F}a$  and  $\mathbf{F}b$  entries in any branch. In addition, a closed tableau can only be achieved after deducing an entry for gate a or gate b. Thus we must have either  $\mathbf{F}a$  or  $\mathbf{F}b$  in every branch. But if we have  $\mathbf{F}a$  or  $\mathbf{F}b$  in every branch, then we effectively have a  $\mathbf{BC}_i$ -refutation for  $C(PHP_n^{n+1})$ . By corollary 3, the size of such a refutation must be exponential in n.

# Theorem 6. $BC_{bu} > BC_{i}$ .

*Proof.* Obviously,  $\mathbf{BC}_{bu} \succeq \mathbf{BC}_{i}$ . By lemma 4, there is a family  $\{\mathcal{C}_{n}\}$  of circuits for which  $\mathbf{BC}_{bu}$  has constant size refutations while the minimal  $\mathbf{BC}_{i}$ -refutations are of exponential size w.r.t. the circuit index n. As the size of the circuit  $\mathcal{C}_{n}$  is  $\mathcal{O}(n^{3})$ , the minimal  $\mathbf{BC}_{i}$ -refutations are of size superpolynomial in the size of the circuit. Based on these facts,  $\mathbf{BC}_{i} \succeq \mathbf{BC}_{bu}$  cannot hold.

# 5.3. $\mathbf{BC}_{i+td}$ vs $\mathbf{BC}_{i}$

We now proceed to show that  $BC_i$  cannot polynomially simulate  $BC_{i+td}$ . This follows directly from the following lemma. In the proof, we re-use the ideas employed in the proof of lemma 4.

**Lemma 5.** There is an infinite family  $\{C_n\}$  of circuits such that (i) the size of  $C_n$  is  $\mathcal{O}(n^3)$ , and (ii) there is a  $\mathbf{BC}_{i+td}$ -refutation for  $C_n$  of constant size while any minimal  $\mathbf{BC}_i$ -refutation for  $C_n$  is of exponential size w.r.t. n.

*Proof.* Consider again the family of circuits of the type shown in figure 11(a). We have that any circuit in the family is unsatisfiable. For  $\mathbf{BC_{i+td}}$  we can construct a constant size refutation by first deducing  $\mathbf{T}e$ , then applying the cut rule on gate a, and then closing each branch similarly to the refutation shown in figure 3. For  $\mathbf{BC_{i}}$ , all  $\mathbf{BC_{i}}$ -refutations will be of exponential size w.r.t. n as argued in the proof of lemma 4.

# Theorem 7. $BC_{i+td} > BC_i$ .

#### 5.4. $\mathbf{BC}_{i+td}$ vs $\mathbf{BC}_{td}$

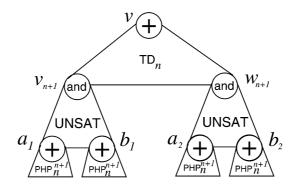

Next we show that  $\mathbf{BC}_{td}$  cannot polynomially simulate  $\mathbf{BC}_{i+td}$  by establishing the following lemma. The proof is based on a circuit constructed from two UNSAT gadgets and a  $TD_n$  gadget.

**Lemma 6.** There is an infinite family  $\{C_n\}$  of circuits such that (i) the size of  $C_n$  is  $\mathcal{O}(n)$ , and (ii) there is a  $\mathbf{BC}_{i+td}$ -refutation for  $C_n$  of linear size while any minimal  $\mathbf{BC}_{td}$ -refutation for  $C_n$  is of exponential size w.r.t. n.

*Proof.* Consider the family of circuits of the type shown in figure 11(b). Any circuit in this family is obviously unsatisfiable. For  $\mathbf{BC}_{i+td}$  we can construct a refutation of linear size w.r.t. n as follows. First apply consecutively the cut rule on gates  $a_1, b_1, a_2, b_2$  in each branch. This induces 16 branches, a constant number. We then have an entry for each of  $a_1, b_1, a_2, b_2$  in every branch. Now we can deduce an entry for  $v_{n+1}$  and  $w_{n+1}$  in each branch. As  $C(\text{UNSAT}_{a,b})$  is unsatisfiable, we can only deduce  $v_{n+1}$  and  $v_{n+1}$ . This can clearly be done in a constant number of steps. From the entries  $v_{n+1}$ ,  $v_{n+1}$  we can then deduce  $v_{n+1}$ , and  $v_{n+1}$ . Proceeding recursively, we can thus deduce  $v_{n+1}$  in every branch with a linear number of steps w.r.t.  $v_{n+1}$ .

Notice that to generate a refutation we need to reach the UNSAT gadgets, as in the proof of lemma 4. But by lemma 1, before reaching the gate  $z_n$  top-down, we already must have generated a tableau with exponentially many entries w.r.t. n. Every  $\mathbf{BC}_{td}$ -refutation is thus of exponential size w.r.t. n for this family of circuits.

Theorem 8.  $BC_{i+td} > BC_{td}$ .

#### 5.5. $\mathbf{BC}_{bu+td}$ vs $\mathbf{BC}_{i+td}$

In this subsection we show that  $\mathbf{BC}_{i+td}$  cannot polynomially simulate  $\mathbf{BC}_{bu+td}$ . Using the ideas in the proof of lemma 4, we construct a circuit from three circuits similar to the one employed in the proofs of lemmas 4 and 5, an  $XOR_n$  gadget, and an expander subcircuit that connects the former four. The expander circuit is an example of a simple nontrivial circuit in which deduction can be propagated through the circuit in a straightforward fashion. It is applied here so that trivial simplification of the circuit is not possible. Lemma 3 is also applied.

**Lemma 7.** There is an infinite family  $\{C_n\}$  of circuits such that (i) the size of  $C_n$  is  $\mathcal{O}(n^3)$ , and (ii) there is a  $\mathbf{BC}_{\text{bu+td}}$ -refutation for  $C_n$  of size  $\mathcal{O}(n^2)$  while any minimal  $\mathbf{BC}_{\text{i+td}}$ -refutation for  $C_n$  is of exponential size w.r.t. n.

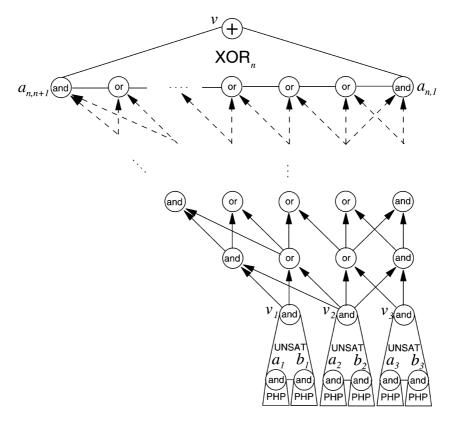

*Proof.* Consider the family of circuits of the type shown in figure 12. Any circuit in the family is unsatisfiable. For  $\mathbf{BC}_{bu+td}$  we can construct a refutation of polynomial

Figure 12. Circuit for theorem 9.

size w.r.t. n as follows. First apply the bottom-up strategy introduced in the proof of lemma 4 to work through the PHP $_n^{n+1}$  gadgets and to generate entries for the and gates  $a_1, a_2, a_3, b_1, b_2, b_3$  in every branch. As in the proof of lemma 4, this can be done having a constant number of entries in the tableau. Then it is straightforward to deduce entries for  $v_1, v_2, v_3$  in each branch. Furthermore, as  $C(\text{UNSAT}_{a,b})$  is unsatisfiable, we must then have  $\mathbf{F}v_1, \mathbf{F}v_2, \mathbf{F}v_3$  in every branch. Now in an arbitrary branch, it is straightforward to deduce the entries  $\mathbf{F}a_{n,j}$  for all  $1 \le j \le n+1$ , generating only a number of entries in the order of  $n^2$ . Continuing on, generating only a number of entries in the order of  $n^2$ , deducing recursively  $\mathbf{F}a_{i-1,j}$  from  $\mathbf{F}a_{i,j}$  and  $\mathbf{F}a_{i,i+1}$  we can at last deduce  $\mathbf{F}v$ . As we have in total a constant number of branches and  $\mathcal{O}(n^2)$  entries in each branch, we clearly have a  $\mathbf{B}\mathbf{C}_{\text{bu+td}}$ -refutation of size  $\mathcal{O}(n^2)$ .

Again, to generate a refutation we need to reach the UNSAT gadgets. With input cuts, this results in a refutation of exponential size w.r.t. n, as argued in the proof of lemma 4. By lemma 3, any top-down approach will also result in a refutation of exponential size w.r.t. n.

Theorem 9.  $BC_{bu+td} > BC_{i+td}$ .

Figure 13. (a) Circuit for theorem 10. (b) Circuit for theorem 11.

## 5.6. **BC**<sub>bu+td</sub> vs **BC**<sub>bu</sub>

Next we show that  $\mathbf{BC}_{bu}$  cannot polynomially simulate  $\mathbf{BC}_{bu+td}$ . In addition to ideas employed in the proof of lemma 5, we use a circuit constructed from a pair of XOR<sub>n</sub> gadgets and an UNSAT gadget, and apply lemma 2.

**Lemma 8.** There is an infinite family  $\{C_n\}$  of circuits such that (i) the size of  $C_n$  is  $\mathcal{O}(n^2)$ , and (ii) there is a  $\mathbf{BC}_{bu+td}$ -refutation for  $C_n$  of constant size while any minimal  $\mathbf{BC}_{bu}$ -refutation for  $C_n$  is of exponential size w.r.t. n.

*Proof.* Consider the family of circuits of the type shown in figure 13(a). As  $C(\text{UNSAT}_{a,b})$  is unsatisfiable, any circuit in this family is also unsatisfiable.

As already described in the proof of lemma 5, for  $\mathbf{BC}_{bu+td}$  we can construct a constant size refutation top–down by first deducing  $\mathbf{T}e$ , then applying the cut rule on gate a, and closing each branch similarly to the refutation shown in figure 3.

It is impossible to generate a refutation without reaching the UNSAT gadgets, as in the previous proofs in which we had an UNSAT gadget as a part of the circuit. By lemma 2, in order to reach the UNSAT gadget, we must generate a tableau with exponential number of branches w.r.t. n. Thus any  $\mathbf{BC}_{bu}$ -refutation for any circuit in this family must be of exponential size w.r.t. n.

**Theorem 10.**  $BC_{bu+td} > BC_{bu}$

#### 5.7. **BC** *vs* **BC**<sub>bu+td</sub>

Now we proceed by showing that  $\mathbf{BC}_{bu+td}$  cannot polynomially simulate  $\mathbf{BC}$ . The proof uses n+1 UNSAT gadgets and 2n+3 XOR $_n$  gadgets, and applies lemmas 2 and 3.

**Lemma 9.** There is an infinite family  $\{C_n\}$  of circuits such that (i) the size of  $C_n$  is  $\mathcal{O}(n^3)$ , and (ii) there is a **BC**-refutation for  $C_n$  of size  $\mathcal{O}(n^2)$  while any minimal **BC**<sub>bu+td</sub>-refutation for  $C_n$  is of exponential size w.r.t. n.

Figure 14. How to generate a polynomial size **BC**-refutation for the circuit shown in figure 13(b).

*Proof.* Consider the family of circuits of the type shown in figure 13(b). For **BC** we can construct a refutation of polynomial size w.r.t. n as follows. First apply the cut rule on  $a_{n,1}$ . In the branch in which we have  $\mathbf{T}a_{n,1}$ , apply the cut rule on  $a_1$ . Similarly to the refutation in figure 3, we can close both the branch in which we have  $\mathbf{T}a_1$  and the one in which we have  $\mathbf{F}a_1$ . In the branch in which we have  $\mathbf{F}a_{n,1}$ , recursively on i, cut first on  $a_{n,i}$  and then in the branch in which we have  $\mathbf{T}a_{n,i}$ , cut on  $a_i$  and again close both of the induced branches. This idea is shown in figure 14. As the refutation in figure 3 is of constant size, we end up with a tableau of linear size w.r.t. n in which there is a single open branch with the entries  $\mathbf{F}a_{n,i}$  for all  $1 \le i \le n+1$ . After this, generating only number of entries in the order of  $n^2$ , deducing recursively  $\mathbf{F}a_{i-1,j}$  from  $\mathbf{F}a_{i,j}$  and  $\mathbf{F}a_{i,i+1}$  we can at last deduce  $\mathbf{F}v$ , thus generating a  $\mathbf{B}\mathbf{C}$ -refutation of size  $\mathcal{O}(n^2)$ .

Again, to generate a refutation we need to reach the UNSAT gadgets. By lemma 2, any bottom—up approach will result in a refutation of exponential size w.r.t. n. By lemma 3, this applies also for any top—down approach. Thus any  $\mathbf{BC}_{bu+td}$ -refutation will be of exponential size w.r.t. n for any circuit in this family.

Theorem 11.  $BC > BC_{bu+td}$ .

## 5.8. **BC**<sub>i</sub> vs **BC**<sub>td</sub>

We now turn to show that  $BC_i$  and  $BC_{td}$  are incomparable under the polynomial simulation relation. The proof draws heavily on the proofs of lemmas 4 and 6.

#### Theorem 12. $BC_i \# BC_{td}$ .

*Proof.* Consider again the family of circuits shown in figure 11(a). In the proof of lemma 4 it is shown that all  $\mathbf{BC_i}$ -refutations for any circuit in this family are of exponential size w.r.t. n. For an idea of how to generate a  $\mathbf{BC_{td}}$ -refutation of constant size we again refer the reader to the refutation shown in figure 3.

On the other hand, consider the family  $\{C_n\}$  of circuits shown in figure 11(b). By the proof of lemma 6 any minimal  $\mathbf{BC}_{td}$ -refutation for  $C_n$  is of exponential size w.r.t. n, while in the same proof it is described how to construct a linear size refutation for  $C_n$  by applying the cut rule only on input gates.

#### 5.9. BC<sub>bu</sub> vs BC<sub>td</sub>

Using ideas from the proof of lemma 8 and theorem 12, we show that  $\mathbf{BC}_{bu}$  and  $\mathbf{BC}_{td}$  are incomparable under the polynomial simulation relation.

#### Theorem 13. $BC_{bu} \# BC_{td}$ .

*Proof.* By theorem 12  $BC_{td}$  cannot polynomially simulate  $BC_i$ . As  $BC_{bu} \succeq BC_i$ ,  $BC_{td}$  cannot polynomially simulate  $BC_{bu}$  either.

Consider the family  $\{C_n\}$  of circuits shown in figure 13(a). It holds that there is a  $\mathbf{BC}_{td}$ -refutation of constant size for each  $C_n$ , while any minimal  $\mathbf{BC}_{bu}$ -refutation is of exponential size w.r.t. n by the proof of lemma 8.

## 5.10. **BC**<sub>bu</sub> vs **BC**<sub>i+td</sub>

As the last one of the main theorems of this work, we argue that  $BC_{bu}$  and  $BC_{i+td}$  are incomparable under the polynomial simulation relation.

## Theorem 14. $BC_{bu} # BC_{i+td}$ .

*Proof.* By theorem 13,  $\mathbf{BC}_{bu}$  cannot polynomially simulate  $\mathbf{BC}_{td}$ . As  $\mathbf{BC}_{i+td} \succeq \mathbf{BC}_{td}$ ,  $\mathbf{BC}_{bu}$  cannot polynomially simulate  $\mathbf{BC}_{i+td}$  either.

On the other hand, consider the family  $\{C_n\}$  of circuits shown in figure 15. Notice that a circuit  $C_n$  consists of a  $TD_n$  gadget from the input gates of which hang two subcircuits equivalent to the circuit in figure 11(a). Combining lemma 1 and the reasoning presented in the proof of lemma 4, we have that every  $\mathbf{BC}_{i+td}$ -refutation for an arbitrary circuit in this family is of exponential size w.r.t. n, as it is impossible to reach the UNSAT gadgets using top-down and input cuts without generating an exponential

Figure 15. Circuit for theorem 14.

number of entries in the tableau w.r.t. n. For  $\mathbf{BC}_{bu}$ , we can generate a refutation of linear size w.r.t. n as follows. It is discussed in the proof of lemma 4 how one can apply the cut on gate a in the circuit in figure 11(a). What we can do here is to cut through the PHP $_n^{n+1}$  circuits similarly as in the proof of lemma 4. Then we can apply the cut rule on each gate  $a_1, b_1, a_2, b_2$  in each branch. After this, it is straightforward to deduce an entry for gates  $v_{n+1}$  and  $w_{n+1}$  in every branch. Due to the unsatisfiability of  $C(\text{UNSAT}_{a,b})$ , with this bottom—up approach it is only possible to deduce  $\mathbf{F}v_{n+1}$ ,  $\mathbf{F}w_{n+1}$ . At this point we note that as the UNSAT gadget with PHP $_n^{n+1}$  gadgets hanging from the input gates has a constant number of gates, we have so far obviously generated a tableau with constant number of entries only. Having  $\mathbf{F}v_{n+1}$ ,  $\mathbf{F}w_{n+1}$  in each branch, it is possible to deduce  $\mathbf{F}v$  by generating only a linear number of entries w.r.t. n, as explained in the proof of lemma 6. Thus we can generate a  $\mathbf{BC}_{bu}$ -refutation of linear size w.r.t. n for any member of the family of circuits considered.

#### 6. Relevance to DPLL

Each Boolean circuit  $\mathcal{C}$  can be translated into a propositional formula in CNF of linear size w.r.t. the size of  $\mathcal{C}$  so that the formula is satisfiable if and only if  $\mathcal{C}$  is. Tseitin's translation [30] is a standard approach, introducing a new variable  $v_g$  for each gate g in  $\mathcal{C}$  and capturing the functional dependencies in  $\mathcal{C}$  by clauses. The translation is summarised in table 1. Clearly, it is linear in the number of gates and edges in  $\mathcal{C}$ . The output CNF formula is the union of the sets of clauses produced by the translation. We now argue that the main results of this work apply to DPLL (without learning or nonchronological backtracking) in the case that the input is in CNF translated from a circuit using Tseitin's translation.

We assume that the reader is familiar with the basic DPLL. A DPLL-refutation can be abstractly seen as a tableau in which the entries are sets of clauses obtained by unit propagation and splitting. A branch in a tableau is contradictory if there are both of the

| i seithi s translation of a boolean circuit to a set of clauses. |                                                                                                              |

|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------|

| Boolean circuit                                                  | Clause set                                                                                                   |

| g is the output gate                                             | $\{(v_g)\}$                                                                                                  |

| $g = not(g_1)$                                                   | $\{(v_g \vee v_{g_1}), (\neg v_g \vee \neg v_{g_1})\}$                                                       |

| $g = \operatorname{or}(g_1, \dots g_k)$                          | $\{(v_{g_1} \vee \cdots \vee v_{g_k} \vee \neg v_g)\} \cup \bigcup_{i=1}^k \{(v_g \vee \neg v_{g_i})\}$      |

| $g = \operatorname{and}(g_1, \dots g_k)$                         | $\{(\neg v_{g_1} \lor \cdots \lor \neg v_{g_k} \lor v_g)\} \cup \bigcup_{i=1}^k \{(\neg v_g \lor v_{g_i})\}$ |

Table 1

Tseitin's translation of a Boolean circuit to a set of clauses

unit clauses (a) and  $(\neg a)$  in the branch for some variable a. The rest of the terminology concerning DPLL-tableaux is synonymous in an obvious way with that of **BC**-tableaux.

For the following, let  $\varphi$  be a set of clauses that is obtained from a Boolean circuit using Tseitin's translation. It holds that DPLL for  $\varphi$  can polynomially simulate **BC** for the original circuit, and vice versa. In fact, any DPLL-refutation can be interpreted as a **BC**-refutation, and vice versa. Especially, we argue that unit clauses  $(v_g)$   $((\neg v_g))$  in a DPLL-refutation correspond exactly to entries  $\mathbf{T}g$   $(\mathbf{F}g)$  of the corresponding **BC**-refutation.

Obviously, the splitting rule in DPLL is equivalent to the cut rule in **BC**; adding the unit clause  $(v_g)$   $((\neg v_g))$ , is equivalent to extending a branch with  $\mathbf{T}g$   $(\mathbf{F}g)$  by applying the cut rule, and vice versa. It is also straightforward to see that the unit propagation rule in DPLL and the deterministic tableau rules in figures 2(b)–(h) in **BC** have equivalent deduction power. To demonstrate this, we consider the two following example cases.

Consider the last undetermined child rule for and gates. Assume a branch in which (i) a gate  $g = \operatorname{and}(g_1, \ldots, g_k)$  is constrained to false by having the entry  $\mathbf{F}g$  and (ii) all  $g_1, \ldots, g_{k-1}$  are constrained to true by having the entries  $\mathbf{T}g_1, \ldots, \mathbf{T}g_{k-1}$ . One can now deduce  $\mathbf{F}g_k$  by applying the rule. This deduction step can be simulated in the corresponding DPLL-tableau branch because the branch has unit clauses  $(\neg v_g), (v_{g_1}), \ldots$ , and  $(v_{g_{k-1}})$ . Thus the clause  $(\neg v_{g_1} \lor \cdots \lor \neg v_{g_k} \lor v_g)$  resulting from Tseitin's translation of and gates can be transformed into the unit clause  $(\neg v_{g_k})$  by applying unit propagation.

On the other hand, assume that it is possible to generate the unit clause  $(\neg v_g)$  in a branch of the DPLL-tableau by unit propagating on an original clause of form  $(v_{g_1} \vee \cdots \vee v_{g_k} \vee \neg v_g)$ . This means that the branch must contain the unit clauses  $(\neg v_{g_1}), \ldots, (\neg v_{g_k})$ . Thus the corresponding **BC**-tableau branch has the entries  $\mathbf{F}g_1, \ldots, \mathbf{F}g_k$  and the entry  $\mathbf{F}g$  can be deduced by applying an "up" rule on the gate  $g = \text{or}(g_1, \ldots, g_k)$  that was translated to have the clause  $(v_{g_1} \vee \cdots \vee v_{g_k} \vee \neg v_g)$  in the CNF formula.

# 7. Conclusion

This work addresses the question of how restrictions on the use of the cut rule affect proof complexity in Boolean circuit satisfiability checking based on tableaux. The

tableau method in question consists of a complete and sound subset of the rules in the method introduced in [18]. The results show that the methods obtained by the cut restrictions considered (any combination of input, top-down, and bottom-up cuts) cannot polynomially simulate the unrestricted method. Moreover, for each pair of restricted methods, there exist a family of circuits  $\{C_n\}$  for which the sizes of the minimal proofs differ exponentially w.r.t. n between the methods.

The introduced tableau method is a nonclausal generalisation of the Davis-Putnam-Logemann-Loveland method for CNF formulas. The results show that DPLL with locality based cut restrictions, such as splitting on the input gates only, cannot polynomially simulate the DPLL method with an unrestricted splitting rule. This, in turn, contradicts a common belief based on empirical results [12,28] that for CNF formulas obtained from a circuit (or formula) representation, a significant gain in efficiency is obtained if splitting is restricted to variables corresponding to input gates (or variables in the original formula).

The results suggest a number of interesting topics of further research. They indicate that good cut heuristics, i.e., general methods for choosing gates on which the cut rule is applied, can have significant impact on efficiency. The total number of gates in a circuit can be enormous compared to the number of input gates. Hence, restricting to input cuts seems to be a computationally attractive alternative. However, our results show that allowing even slightly more general cuts can lead to significant savings. The key research question is how to limit the subset of gates on which to apply the cut, and how to choose a good cut among the candidates so that the attractive computational properties are preserved. In order to evaluate empirically the theoretical results of the paper such new cut heuristics for CIRCUIT SAT need to be developed and implemented. Secondly, modern SAT solvers employ a number of search space pruning techniques, like one-step lookahead, equivalence reasoning, cone-of-influence (see, e.g., [18]) as well as non-chronological backtracking and learning schemes (see, e.g., [24,29,31]). An interesting question is how proof complexity is affected by these techniques.

#### References

- [1] P. Beame, R. Karp, T. Pitassi and M. Saks, The efficiency of resolution and Davis–Putnam procedures, SIAM Journal on Computing 31(4) (2002) 1048–1075.

- [2] P. Beame and T. Pitassi, Propositional proof complexity: Past, present, and future, Bulletin of the European Association for Theoretical Computer Science 65 (1998) 66–89.

- [3] A. Biere and W. Kunz, SAT and ATPG: Boolean engines for formal hardware verification, in: *Proc.* of the 20th IEEE/ACM International Conference on Computer Aided Design (2002) pp. 782–785.

- [4] P. Bjesse, T. Leonard and A. Mokkedem, Finding bugs in an alpha microprocessor using satisfiability solvers, in: *Proc. of the 13th International Conference of Computer-Aided Verification*, Lecture Notes in Computer Science, Vol. 2102 (Springer, New York, 2001) pp. 454–464.

- [5] E. Clarke, A. Biere, R. Raimi and Y. Zhu, Bounded model checking using satisfiability solving, Formal Methods in System Design 19(1) (2001) 7–34.

- [6] M. D'Agostino, D.M. Gabbay, R. Hähnle and J. Posegga, eds., *Handbook of Tableau Methods* (Kluwer Academic, Dordrecht, 1999).

- [7] M. D'Agostino and M. Mondadori, The taming of the cut: Classical refutations with analytic cut, Journal of Logic and Computation 4(3) (1994) 285–319.

- [8] E. Dantsin, A. Goerdt, E.A. Hirsch, R. Kannan, J. Kleinberg, C. Papadimitriou, P. Raghavan and U. Schöning, A deterministic  $(2-2/(k+1))^n$  algorithm for k-SAT based on local search, Theoretical Computer Science 289(1) (2002) 69–83.

- [9] M. Davis, G. Logemann and D. Loveland, A machine program for theorem proving, Communications of the ACM 5(7) (1962) 394–397.

- [10] M. Davis and H. Putnam, A computing procedure for quantification theory, Journal of the ACM 7(3) (1960) 201–215.

- [11] M. Ganai, L. Zhang, P. Ashar, A. Gupta and S. Malik, Combining strengths of circuit-based and CNF-based algorithms for a high-performance SAT solver, in: *Proc. of the 39th Conference on Design Automation* (2002) pp. 747–750.

- [12] E. Giunchiglia, A. Massarotto and R. Sebastiani, Act, and the rest will follow: Exploiting determinism in planning as satisfiability, in: *Proc. of the 15th National Conference on Artificial Intelligence and of the 10th Conference on Innovative Applications of Artificial Intelligence* (1998) pp. 948–953.

- [13] E. Giunchiglia and R. Sebastiani, Applying the Davis—Putnam procedure to non-clausal formulas, in: *Proc. of the Italian National Conference on Artificial Intelligence* (2000) pp. 84–94.

- [14] J. Gu, P.W. Purdom, J. Franco and B.W. Wah, Algorithms for the satisfiability (SAT) problem: A survey, in: *Satisfiability Problem: Theory and Applications*, eds. D. Du, J. Gu and P.M. Pardalos, Discrete Mathematics and Theoretical Computer Science, Vol. 35 (Amer. Math. Soc, Providence, RI, 1997) pp. 19–152.

- [15] A. Haken, The intractability of resolution, Theoretical Computer Science 39(2/3) (1985) 297–308.

- [16] S. Jukna, Extremal Combinatorics: With Applications in Computer Science (Springer, Berlin, 2001).

- [17] T.A. Junttila, BCSat 0.3 a satisfiability checker for Boolean circuits, Computer program (2001), available at http://www.tcs.hut.fi/Software/.

- [18] T.A. Junttila and I. Niemelä, Towards an efficient tableau method for Boolean circuit satisfiability checking, in: *Computational Logic CL 2000; First International Conference*, Lecture Notes in Artificial Intelligence, Vol. 1861 (Springer, Berlin, London, UK, 2000) pp. 553–567.

- [19] H. Kautz and B. Selman, Planning as satisfiability, in: *Proc. of the 10th European Conference on Artificial Intelligence* (1992) pp. 359–363.

- [20] H. Kautz and B. Selman, Pushing the envelope: Planning, propositional logic, and stochastic search, in: Proc. of the 13th National Conference on Artificial Intelligence (1996) pp. 1194–1201.

- [21] A. Kuehlmann, M.K. Ganai and V. Paruthi, Circuit-based Boolean reasoning, in: *Proc. of the 38th Conference on Design Automation* (2001) pp. 232–237.

- [22] T. Larrabee, Test pattern generation using Boolean satisfiability, IEEE Transactions on Computer-Aided Design 11(1) (1992) 6–22.

- [23] J.P. Marques-Silva and L.G. e Silva, Solving satisfiability in combinational circuits, IEEE Design & Test of Computers 20(4) (2003) 16–21.

- [24] J.P. Marques-Silva and K.A. Sakallah, GRASP: A new search algorithm for satisfiability, in: Proc. of the 1996 IEEE/ACM International Conference on Computer-Aided Design (1997) pp. 220–227.

- [25] F. Massacci, Simplification a general constraint propagation technique for propositional and modal tableaux, in: *Proc. of the International Conference on Automated Reasoning with Analytic Tableaux and Related Methods* (1998) pp. 217–231.

- [26] C.H. Papadimitriou, Computational Complexity (Addison-Wesley, Reading, MA, 1994).

- [27] D.A. Plaisted and S.A. Greenbaum, A structure-preserving clause form translation, Journal of Symbolic Computation 2 (1986) 193–304.

- [28] O. Shtrichman, Tuning SAT checkers for bounded model checking, in: Computer Aided Verification CAV 2000; 12th International Conference, Lecture Notes in Computer Science, Vol. 1855 (Springer, New York, 2000) pp. 480–494.

- [29] C. Thiffault, F. Bacchus and T. Walsh, Solving nonclausal formulas with DPLL search, in: *Proc. of the 10th International Conference on Principles and Practice of Constraint Programming* (2004) pp. 663–678.

- [30] G.S. Tseitin, On the complexity of derivation in propositional calculus, in: *Automation of Reasoning 2: Classical Papers on Computational Logic 1967–1970*, eds. J. Siekmann and G. Wrightson (Springer, Berlin, 1983) pp. 466–483.

- [31] L. Zhang, C.F. Madigan, M.W. Moskewicz and S. Malik, Efficient conflict driven learning in Boolean satisfiability solver, in: *Proc. of the International Conference on Computer Aided Design* (2001) pp. 279–285.

- [32] L. Zhang and S. Malik, The quest for efficient Boolean satisfiability solvers, in: *Automated Deduction CADE-18*, Lecture Notes in Computer Science, Vol. 2392 (Springer, New York, 2002) pp. 295–313.