## Virtual Memory (VM) Ch 83

Memory Management Address Translation Paging Hardware Support VM and Cache

(virtuaalimuisti)

18 9 2003 Copyright Teemu Kerola 2003

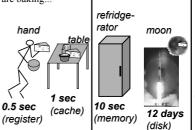

## Teemu's Cheesecake

Register, on-chip cache, memory, disk, and tape speeds relative to times locating cheese for the cheese cake you are baking... Europa

(Jupiter)

(tape)

18 9 2003 Copyright Teemu Kerola 2003

## Virtual Memory

• Problem: How can I make my (main) memory as big as my disk drive?

- · Answer: Virtual memory

- keep only most probably referenced data in memory, and rest of it in disk

- disk is much bigger and slower than memory

- · address in machine instruction may be different than memory address

- · need to have efficient address mapping

- · most of references are for data in memory

- joint solution with HW & SW

18 9 2003 Copyright Teemu Kerola 2003

## Other Problems Often Solved with VM (3)

- If you must want to have many processes in memory at the same time, how do you keep track of memory usage?

- How do you prevent one process from touching another process' memory areas?

- What if a process needs more memory than we have?

18 9 2003 Copyright Teemu Kerola 2003

## Memory Management Problem (4)

- How much memory for each process?

- is it fixed amount during the process run time or can it vary during the run time?

- Where should that memory be?

- in a continuous or discontinuous area?

- is the location the same during the run time or can it vary dynamically during the run time?

- How is that memory managed?

- How is that memory referenced?

18 9 2003 Copyright Teemu Kerola 2003

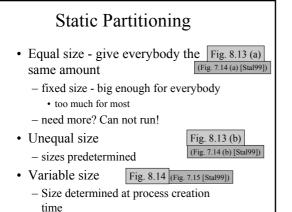

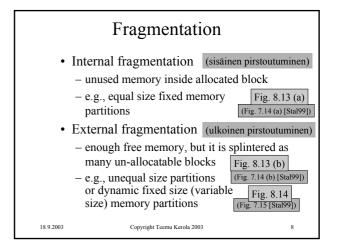

## Partitioning (3)

- How much physical memory for each process?

- Static (fixed) partitioning kiinteät partitiot)

(staattiset tai

- amount of physical memory determined at process creation time

- continuous memory allocation for partition

- Dynamic partitioning

(dynaamiset partitiot)

- amount of physical memory given to a process varies in time

- due to process requirements (of this process)

- due to system (I.e., other processes) requirements

18 9 2003

Copyright Teemu Kerola 2003

## Dynamic Partitioning (3)

Copyright Teemu Kerola 2003

- Process must be able to run with <u>varying</u> <u>amounts</u> of main memory

- all of memory space is **<u>not</u>** in physical memory

- need some minimum amount of memory

- · New process?

18 9 2003

- reduce amount of memory for some (lower priority) processes

- Not enough memory for some process?

- reduce amount of memory for some (lower priority) processes

- kick (swap) out some (lower priority) process

18.9.2003 Copyright Teemu Kerola 2003

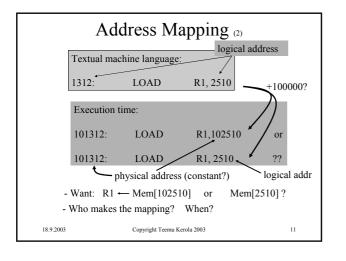

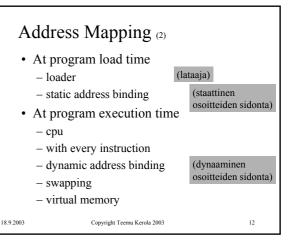

Address Mapping (4) (osoitteen muunnos) Pascal, Java: Symbolic Assembler: while (....) R1. Y loop: LOAD X := Y + ZADD R1, Z**STORE** R1, X Textual machine language: Execution time: 1312: LOAD R1, 2510 ADD R1, 2514 101312: LOAD R1,102510 STORE R1, 2600 ADD R1.102514 ADD R1,102600 (addresses relative to 0) (real, actual!) 18 9 2003 Copyright Teemu Kerola 2003

## Swapping (4)

(heittovaihto)

13

15

17

- Keep <u>all memory areas</u> for all running and ready-to-run processes in memory

- · New process

- find continuous memory partition and swap the process in

- Not enough memory?

- Swap some (lower priority) process out

- Some times can swap in only (runnable) portions of one process

- Address map: add base address

18.9.2003 Copyright Teemu Kerola 2003

## VM Implementation (2)

- Methods

- base and limit registers

- segmentation

- paging

- segmented paging, multilevel paging

- Hardware support

- MMU Memory Management Unit

- · part of processor

- · varies with different methods

- Sets limits on what types of virtual memory (methods) can be implemented using this HW

18.9.2003

Copyright Teemu Kerola 2003

## Base and Limit Registers (2)

- Continuous memory partitions

- one or more (4?) per process

- may have separate base and limit registers

- · code, data, shared data, etc

- · by default, or given explicitly in each mem. ref.

- BASE and LIMIT registers in MMU

- all addresses logical in machine instructions

- address mapping for address (x):

- check: x < LIMIT

- physical address: BASE+x

18.9.2003

Copyright Teemu Kerola 2003

## Segmentation (4)

- Process address space divided into (relatively large) logical segments

- code, data, shared data, large table, etc

- object, module, etc

- Each logical segment is allocated its own continuous physical memory segment

- · Memory address has two fields

011001 1010110000

segment byte offset

(lisäys)

18.9.2003

18 9 2003

Copyright Teemu Kerola 2003

# Segment. Address Mapping (3)

- Segment table

- maps segment id to physical segment base address and to segment size

- Physical address

- find entry in segment table

- check: byte offset < segment size</p>

- physical address: base + byte offset

- Problem: variable size segments

- External fragmentation, lots of memory management

18.9.2003 Cop

Copyright Teemu Kerola 2003

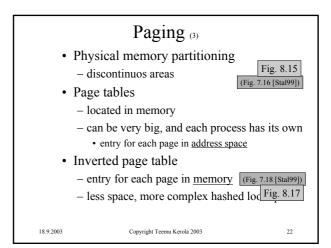

# Paging (4)

- Process address space divided into (<u>relatively small</u>) equal size <u>pages</u>

- address space division is not based on logical entities, only on fixed size chunks designed for efficient implementation

- Each page is allocated its own physical page frame in memory

- any page frame will do!

- Internal fragmentation

- Memory addresses have two fields

01100110 10110000

page byte offset

(lisäys)

Copyright Teemu Kerola 2003

18

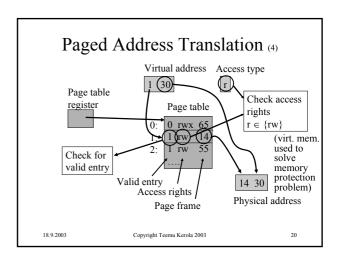

## Paged Address Mapping

- Page table

- maps page nr to physical page frame

- Physical address

- find entry in page table (large array in memory)

19

- get page frame, I.e., page address

- physical address: page address + byte offset

18.9.2003 Copyright Teemu Kerola 2003

# Address Translation (3)

- MMU does it for every memory access

- code, data

- more than once per machine instruction!

- Can not access page tables in memory every time - it would be too slow!

- too high cost to pay for virtual memory?

- MMU has a "cache" of most recent address translations

(osoitteenmuunnostaulukko)

23

- TLB - Translation Lookaside Buffer

- 99.9% hit ratio?

18.9.2003 Copyright Teemu Kerola 2003

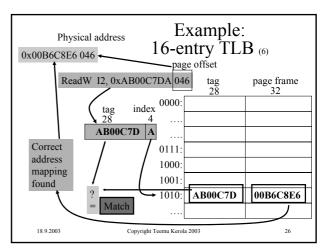

## Translation Lookaside Buffer (3)

Fig. 8.18 (Fig. 7.19 [Stal99])

- · "Hit" on TLB?

- address translation is in TLB real fast

- · "Miss" on TLB?

- must read page table entry from memory

- takes time

- cpu waits idle until it is done

- Just like normal cache, but for address mapping

- implemented just like cache

- instead of cache line data have physical address

- split TLB? 1 or 2 levels?

18.9.2003 Copyright Teemu Kerola 2003 24

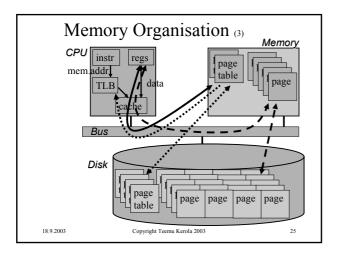

### TLB and Cache (3)

- Usually address translation first Fig. 8.19 and then cache lookup (Fig. 7.20 [Stat199])

- Cache can be based on virtual addresses

- can do TLB and cache lookup simultaneously

- faster

- Implementations are very similar

- TLB often fully associative

- optimised for temporal locality (of course!)

18.9.2003 Copyright Teemu Kerola 2003

#### TLB vs. Cache

#### TLB Miss

- · CPU waits idling

- HW implementation

- · Invisible to process

- Data is copied from memory to TLB

- from page table data

- from cache?

- Delay 4 (or 2 or 8?) clock cycles

#### Cache Miss

- · CPU waits idling

- HW implementation

- Invisible to process

- Data is copied from memory to cache

- · from page data

- Delay 4 (or 2 or 8?) clock cycles

18.9.2003 Copyright Teemu Kerola 2003 28

## TLB Misses vs. Page Faults

Copyright Teemu Kerola 2003

#### TLB Miss

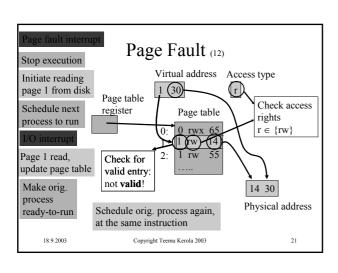

#### Page Fault

- CPU waits idling

- HW implementation

- Data is copied from memory to TLB (or from cache)

- Delay 1-4 (?)

18 9 2003

- Process is suspended and cpu executes some other process

- SW implementation

- Data is copied from disk to memory

- Delay 30 ms (?)

2.7

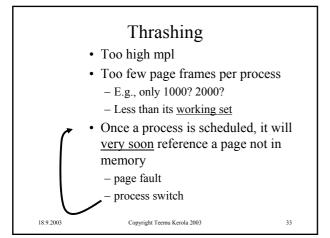

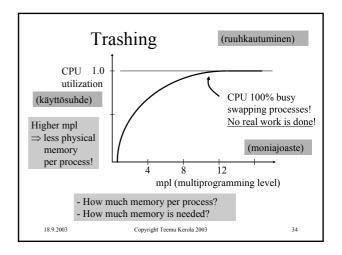

## Virtual Memory Policies (3)

- · Fetch policy

- (noutopolitiikka)

- demand paging: fetch page only when needed 1st time

- working set: keep all needed pages in memory

- prefetch: guess and start fetch early

- Placement policy

- any frame for paged VM

#### (sijoituspolitiikka)

- any name for paged vi

- Replacement policy

#### (poistopolitiikka)

- local, consider pages just for this process for replacement

- global, consider also pages for all other processes

- dirty pages must be written to disk

(likaiset, muutetut)

18.9.2003 Copyright Teemu Kerola 2003

30

## Page Replacement Policy (2)

- Implemented in SW

- · HW support

- extra bits in each page frame

- M = Modified

- -R = Referenced

- set (to 1) with each reference to frame

- reset (to 0) every now and then

- special (privileged) instruction from OS

- automatically (E.g., every 10 ms)

- Other counters?

18.9.2003 Copyright Teemu Kerola 2003

Page Replacement Policies (6)

• OPT - optimal

(sivunpoistoalgoritmit)

- · NRU not recently used

- FIFO first in first out

- 2nd chance

- clock

OS Virtual Memory Management

- Random

- · LRU least recently used

- complex counter needed

- NFU not frequently used

18 9 2003

31

Copyright Teemu Kerola 2003

32

# Page Fault Frequency (PFF) <a href="Dynamic">Dynamic</a> Memory Allocation

- Two bounds: L=Lower and U=Upper

- Physical memory split into fixed size pages

- At every page fault

- T=Time since previous page fault

- if T<L then give process more memory

- 1 page frame? 4 page frames?

- if U<T then take some memory away</li>

- · 1 page frame?

- if L<T<U then keep current allocation

18.9.2003 Copyright Teemu Kerola 2003

# Multi-level paging/segmentation

Segmented paging

01101 01100110 10110000

address logically split

segm page byte offset

- into segments and then physically into pages

- protection may be at segment level

- · Multiple level paging

- large address space may result in very large page tables

- solution: multiple levels of page tables

Fig. 5.43 [HePa96]

- VM implementation may not utilize them all

- VM implementation may seem to use more levels than there are (e.g., Linux 3 levels on 2-level Intel arch.)

- · nr of actual levels in mem. management macros

18.9.2003 Copyright Teemu Kerola 2003 36

## VM Summary

- How to partition memory?

- Static or dynamic size (amount)

- How to allocate memory

- Static or dynamic location

- · Address mapping

- HW help (TLB) for address translation

- before or concurrently with cache access?

- · VM policies

- fetch, placement, replacement

18.9.2003

Copyright Teemu Kerola 2003

37

Fig. 5.47 from Fully assoc, Hennessy-Patterson, 32 entry Computer Architecture data TLB Alpha AXP 21064 memory hierarchy 8 KB, direct Fully assoc, 12 entry mapped, instruction TLB 256 line (each 32B) 8 KB, direct mapped data cache 256 line (each 32B) instruction cache main memory 2 MB, 64K line (each 32B) direct mapped, unified, write-back L2 cache paging disk (dma) Copyright Teemu Kerola 2003

-- End of Chapter 8.3: Virtual Memory --